# Exostiv Presentation & Demo

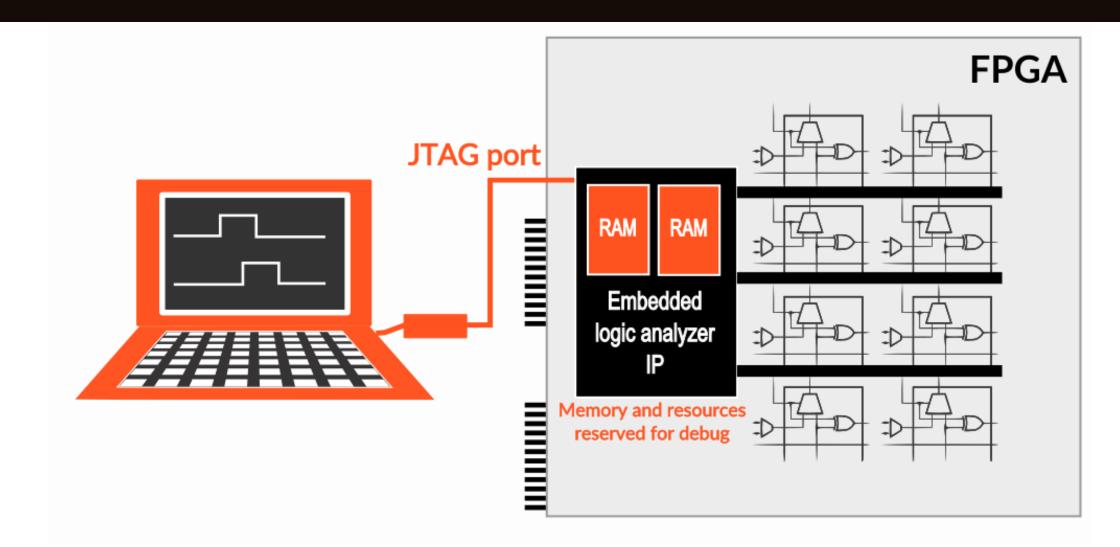

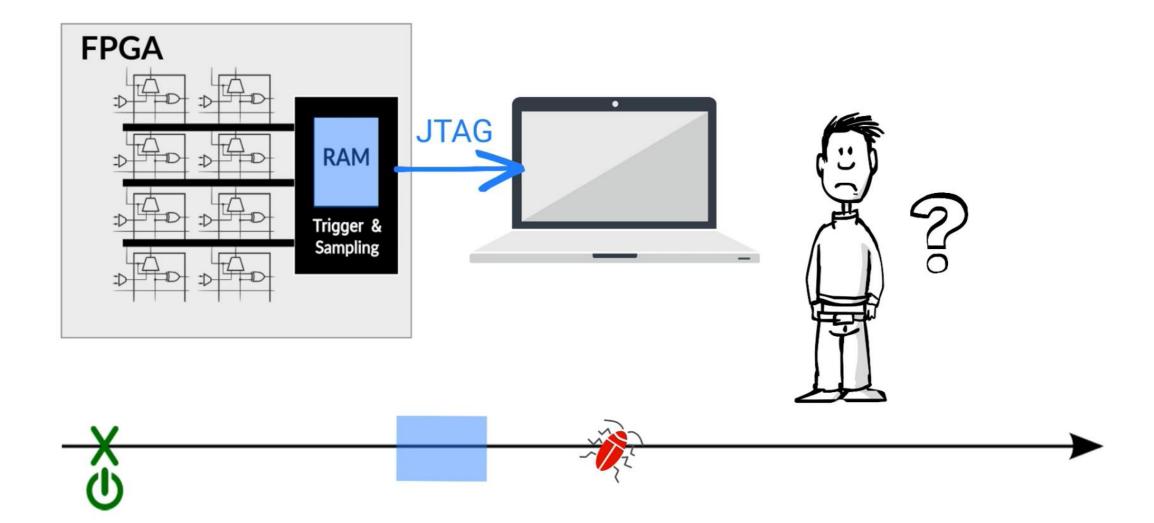

# Debugging with a JTAG solution

# **EXOSTIV**

#### **EXOSTIV - Overview**

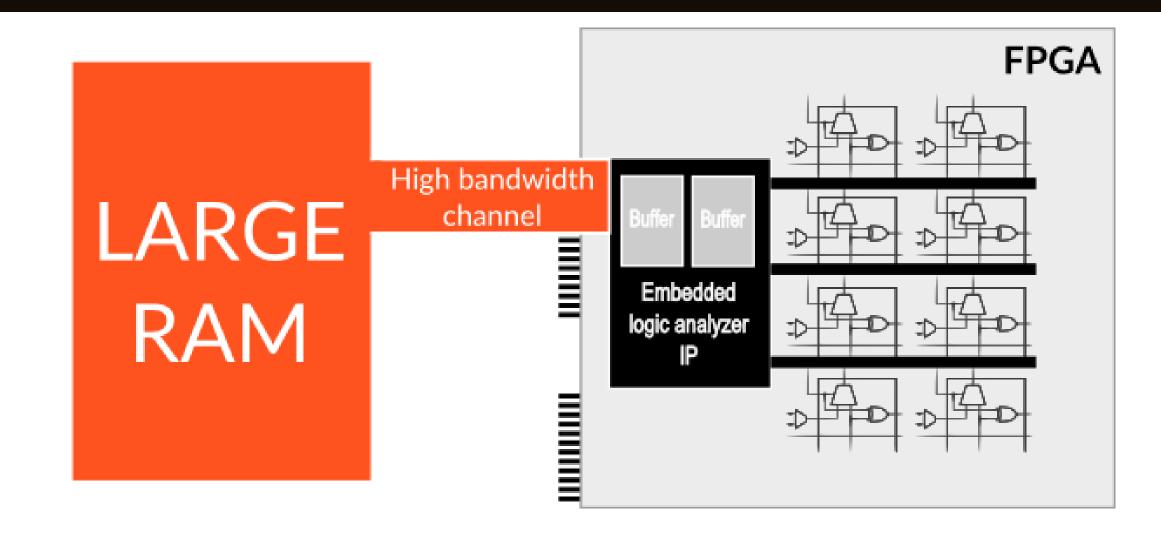

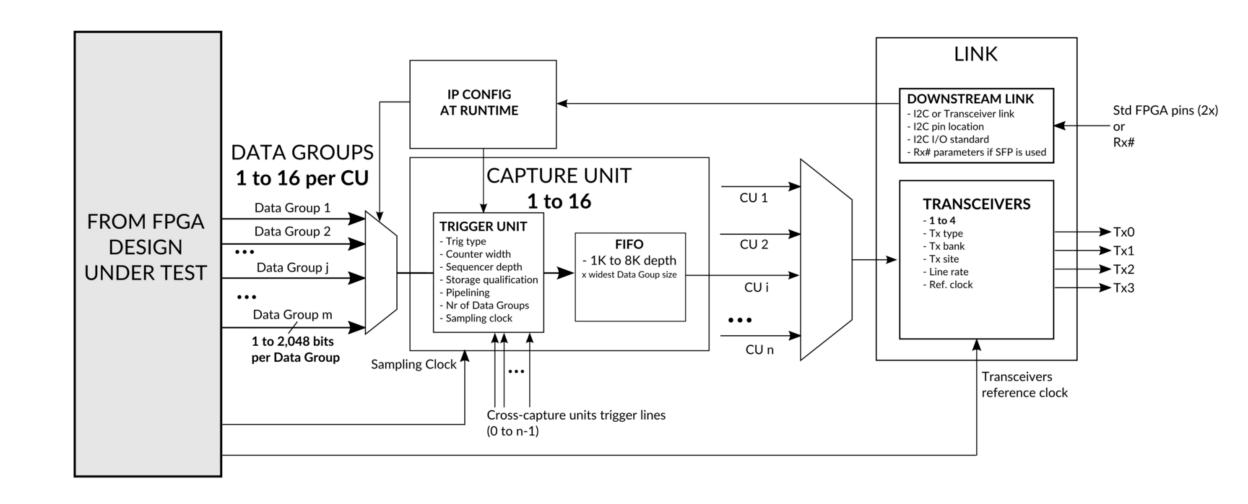

#### Reach internal nodes

- Up to 16 capture units

- Up to **16 data sets** per CU

- 1 trigger + 1 qualification unit per CU

- Up to **2.048 nets** per data set

- IP RAM does not grow with capture size

- Sampling @ system speed

#### **Extract trace**

- Up to 8 GB for trace storage

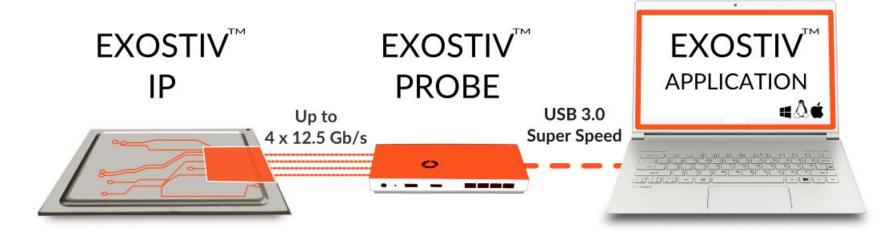

- Up to 4 x 12.5 Gbps bandwidth

- Uses Multi Gigabit Transceivers

- **HDMI** and **SFP+** cage connector

- Optional connector adapters

- Downstream channel for IP control

- **USB 3.0** connection with workstation

#### **Control & Analyze**

- IP configuration & insertion

- Trigger and data filter set up

- IP communication and control

- Trace reception and encoding

- Advanced waveform viewer

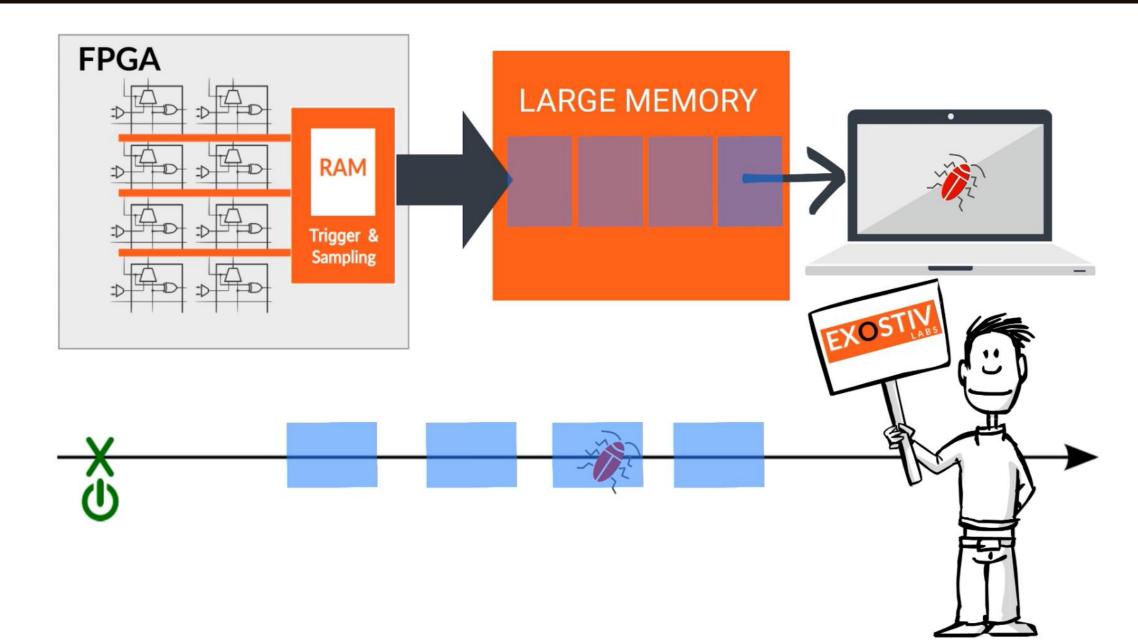

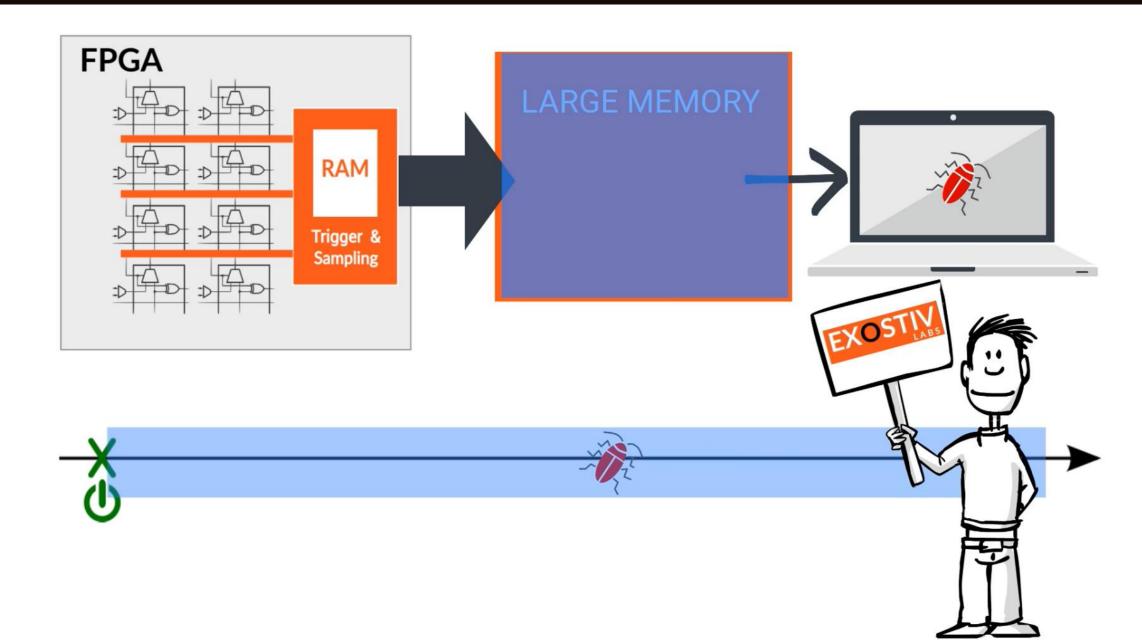

# Indicative gain

#### OBSERVABLE OPERATING TIME\*

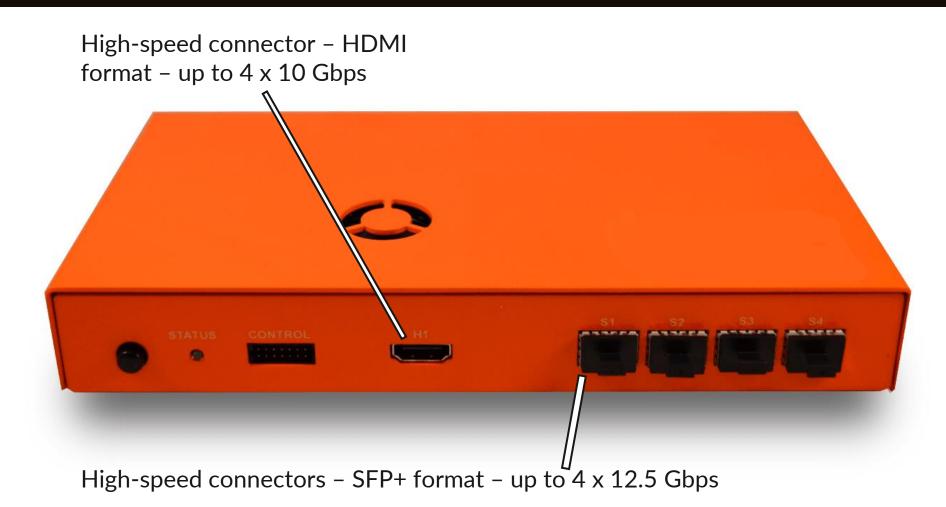

## **EXOSTIV** Probe

# Connectivity

SFP+ or QSFP+ (copper / fiber)

FMC HPC / LPC (with adapter)

(New connectors under qualification – Samtec, ...)

Custom low footprint

FMC / QSFP connectivity

# Custom low footprint connectivity

# QSFP+ connectivity

# Choose the board you like

- Pick a standard FPGA board

- Xilinx development kits

- Intel development kits

- The Dini Group / Synopsys

- proFPGA

- High Tech Global

- Enclustra

- REFLEX CES

- •

- Use a FPGA board designed in-house

- Add a custom connector

- Use an existing connector, possibly with an adapter (See the Connecting Guide)

https://www.exostivlabs.com/support/fpga-boards/

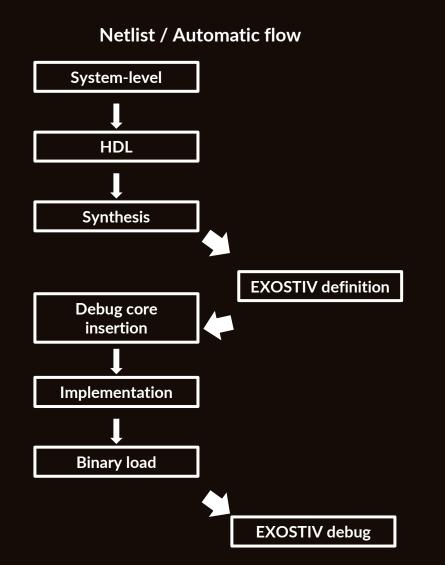

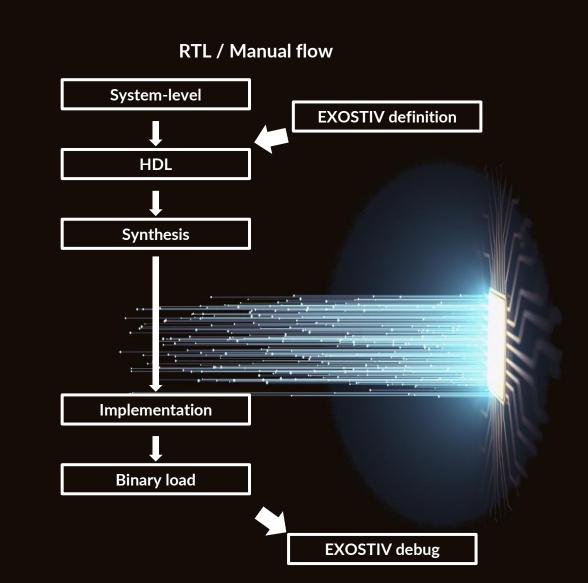

### IP insertion flows

#### **IP** Overview

## **EXOSTIV**

- 32K nodes per FPGA max

- 8 GB memory

- 50 Gbps bandwidth

- > 350 MHz operation

- Data multiplexing, triggering, filtering, event counters

- Integrated waveform viewer

- Xilinx Series 7, Ultrascale(+), Zynq / Intel Series 10 support

# Thank you.