EXOSTIV IP

Please go to the respective product pages for information about the IP generated with software v2 for the EP16000 Probe or Exostiv Blade

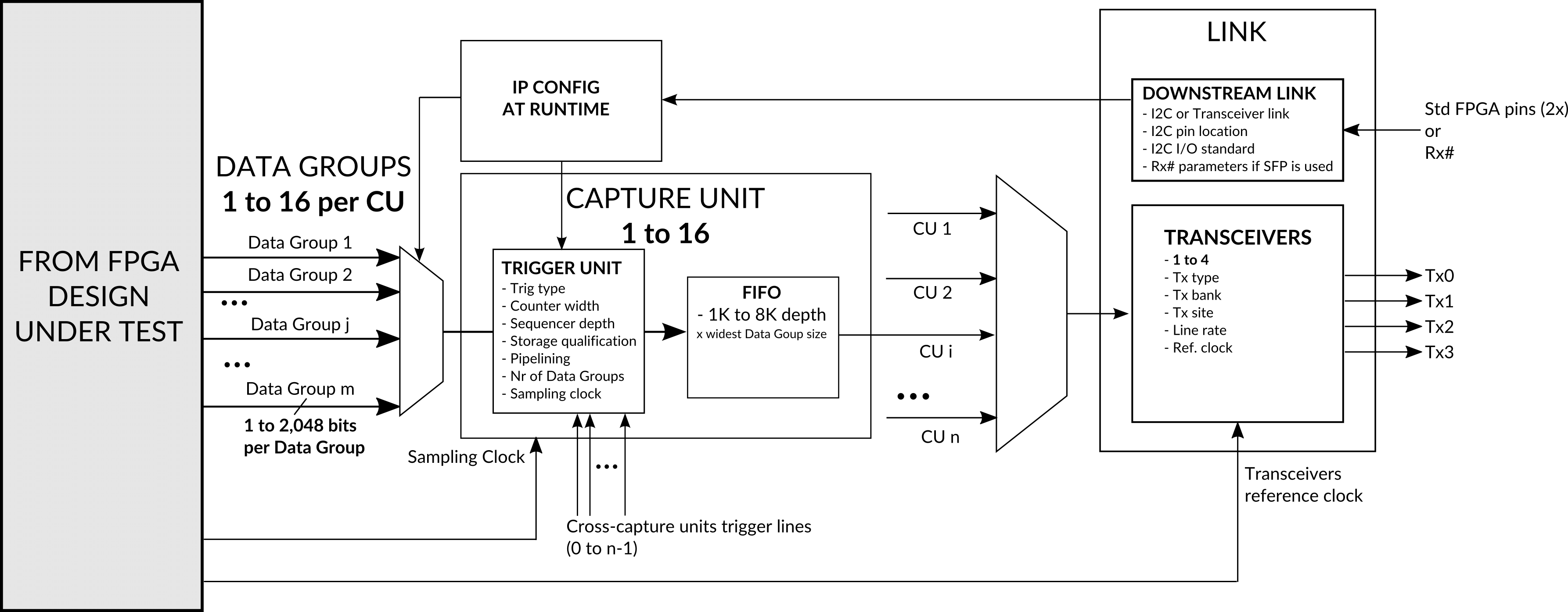

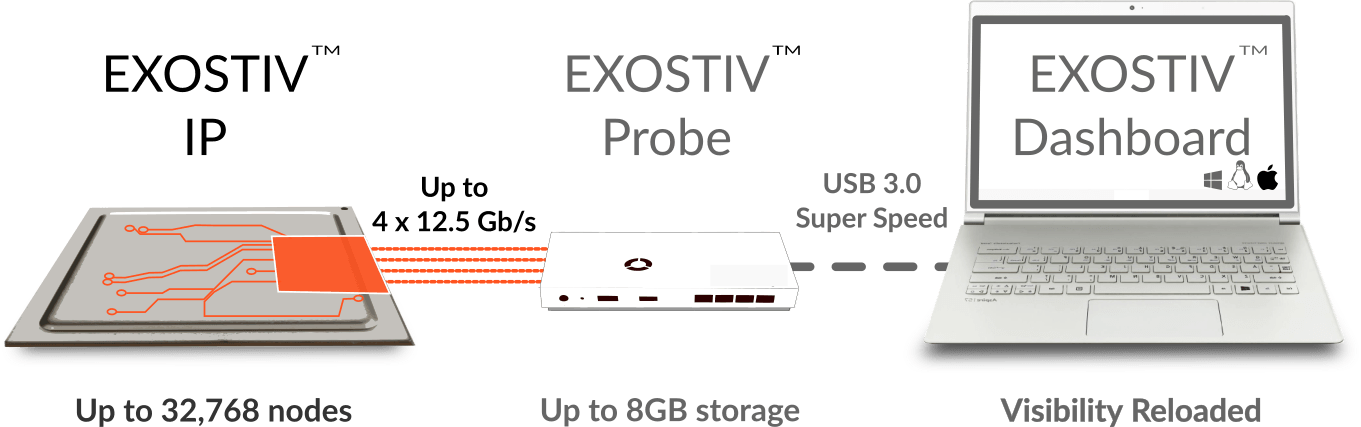

The customizable EXOSTIV IP core is a logic analyzer core that can be used to monitor the internal signals of an FPGA design without having to store the full trace data in the FPGA. The EXOSTIV IP core uses the FPGA transceivers as a high bandwidth channel to an external memory (in EXOSTIV Probe). The EXOSTIV IP core must always be used together with the EXOSTIV Probe and EXOSTIV Dashboard software.

The IP includes many advanced features for extending visibility on FPGA running at speed of operation- including data group definition and multiplexing, boolean trigger equations, data qualification (data filtering) and edge transition triggers. Because EXOSTIV IP core is synchronous to the design being monitored, all design clock constraints that are applied to your design are also applied to the components inside IP Core. EXOSTIV IP can be inserted at RTL level or automatically in the design netlist, thanks to the accompanying EXOSTIV Dashboard software.

Features

- Configurable upstream link, using 1 to 4 FPGA transceivers up to 12.5 Gbps located in the same quad or 6 pack.

- Downstream link to configure IP at run-time, without the need to re-implement instrumented design.

- From 1 to 16 configurable ‘Capture Units’ (CU) to sample FPGA internal nodes, with trigger and data qualification resources and selectable FIFO size.

- From 1 to 16 multiplexed Data Groups per CU, selectable at run time through downstream link.

- From 16 to 2,048 bits per Data Group, connected to the target FPGA internal nodes.

- Up to 390 MHz sampling in FPGA.

- Cross-Capture Units trigger lines.

- Limited footprint on FPGA resources – equivalent to the footprint JTAG embedded logic analyzers on the logic for equivalent number of nodes connected. Huge gain on internal memory – FPGA BRAM memory resources do not have to grow with the size of the capture.