Large trace storage is a game changer for FPGA debug.

FPGA programmability has traditionally enabled engineers to use board prototypes in the lab for debug and verification. Using a system at speed in its ‘real’ environment is used to overcome modeling errors and excessive simulation times. Embedded instrumentation utilizing BRAM readback with JTAG is affordable, readily accessible, and simple to configure. All necessary components are supplied by the FPGA chip itself (such as internal block RAM) and the FPGA vendor’s tools. There’s no requirement for additional tools or interfaces.

However, the crucial aspect is effective debugging. A tool that, despite being easy to implement, requires endless iterations can significantly impede productivity, thereby hindering your capacity to deliver high-quality systems for production.

Both scenarios will inevitably result in expensive iterations: either to capture a different set of nodes or to attempt to pinpoint the exact set of trigger conditions within the extremely limited capture window. This is resolved if a much larger memory is used.

With storage limited to a few kilobytes of blockram capacity, you’ll have to manage a ‘number of observed nodes vs. depth’ trade-off.

|  |

Small trace memory leads to time-consuming iterative nodes reconnections | A large external memory enables connecting all desired nodes in one iteration. |

Upscale your tools, don’t downscale your expectations

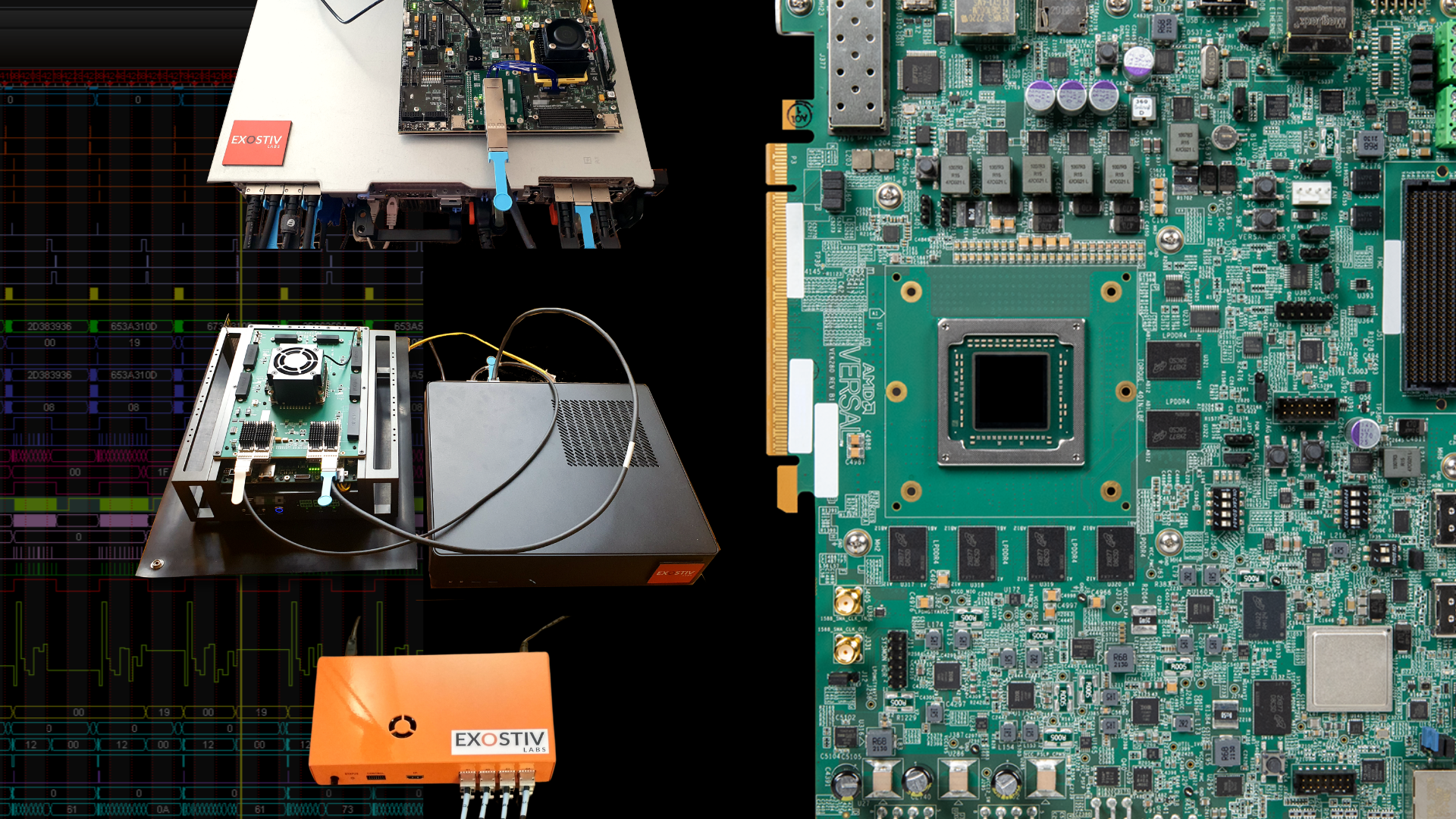

You can sidestep the need to choose between accessing nodes and capturing depth by placing the trace memory in an external storage and utilizing a high-bandwidth channel to extract data from the FPGA. Exostiv Labs offers these tools, along with the required software environment, to effortlessly instrument FPGA and handle extensive debug datasets.

A practical case where large trace memory is a must.

Massive real-time data capture, a game changer to prevent bug escapes to production

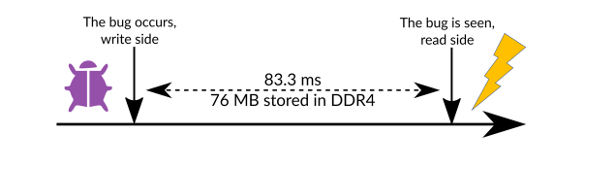

Video processing systems often make use of FPGA coupled with DDR memory as a frame buffer and run processing both on the write and read side of the memory. These systems are characterized with massive and high speed data flow and the latency introduced by the write / read operation to the external DDR memory.

In this webinar replay, we demonstrate why massive real time data capture capabilities are necessary to resolve a difficult bug case.

Our solutions for FPGA Debug

|  |  | ||

Exostiv | Exostiv Blade - Compact chassis | Exostiv Blade - Tower chassis | Exostiv Blade - 2U chassis | Exostiv Blade - 4U chassis |

|

|

|

|

|