Massive Real-time FPGA Data Capture

A game-changer to prevent bug escapes to production.

Welcome to this recorded session – thank you for your interest.

If you are using AMD Ultrascale™(+) devices then you will be fully aware of the complexity of the designs these FPGAs can hold and the considerable time and effort required to verify the functionality. Even with all the modern design verification techniques available, and extensive lab testing, it is estimated that over 80% of the FPGAs in products released to market have non-trivial bugs.

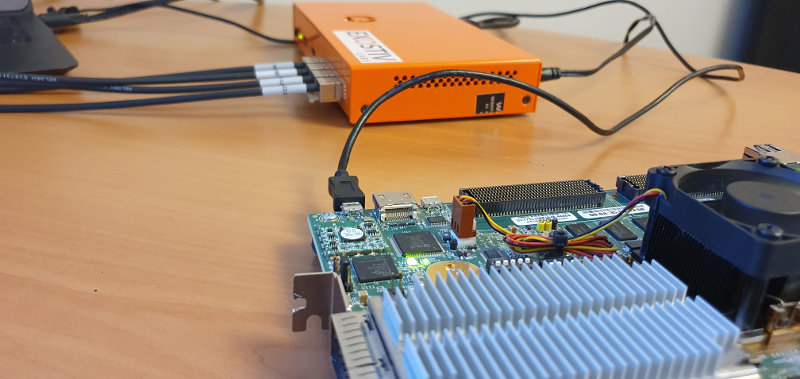

Exostiv provides easy to implement real-time analysis and debug for your Ultrascale(+) designs with seamless integration into the AMD Vivado™ development flow. The massive data capture size provided by Exostiv means that rather than snippets of a designs operation being available for analysis, meaningful periods of running designs can be captured for performance, functionality and debug purposes.

In this webinar, we demonstrate in an example how Exostiv can help you navigate the complexity of advanced FPGA designs and how you can take advantage of its unique features to stop risking to send bug to production.

Thank you for watching.

– Frederic.