Search

Vivado DRC error – PLDS-1 rule violation encountered. What does this mean?

While running netlist-level Exostiv IP insertion, the following error has been reported while running the DRC check after synthesis and before implementation / (P&R):

+———–+———-+———————————————————————+————+

| Rule | Severity | Description | Violations |

+———–+———-+———————————————————————+————+

| PLDS-1 | Error | DSP Connectivity Checks | 6 |

+———–+———-+———————————————————————+————+

PLDS-1#1 Error

DSP Connectivity Checks

Unroutable DSP cascade connection found./…/

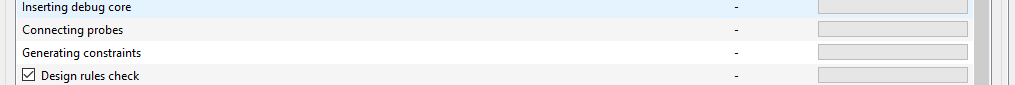

Background: Exostiv Dashboard provides an optional DRC check before running instrumented design implementation in netlist insertion mode (see screenshot below).

This DRC is run on the entire design and can report about items that do not below to Exostiv IP, such as the above error. If you encounter this error, it means that this check fails for DRC run after synthesis and before implementation. The above error is not about EXOSTIV IP, as EXOSTIV IP does not make use of DSP blocks.

It seems that this error is not reported by Vivado when running the DRC after P&R / implementation. If you’d like to know more about, please check with your local Xilinx FAE.

What can you do if you encounter this error while running EXOSTIV IP insertion?

– Each time a DRC error is reported in EXOSTIV Dashboard, you have the choice to ignore it and continue with the implementation. We suggest that you run a DRC after implementation to check if your design still contains this DRC error after implementation. *** This DRC check error is not introduced by EXOSTIV IP ***. It is possible that you see it while using Exostiv Dashboard because we run the DRC right after synthesis, and because your usual design flow calls DRC after implementation.

– Unselect the execution of the DRC check in the EXOSTIV Dashboard ‘Insert EXOSTIV IP’ flow. You will skip the DRC completely.