EXOSTIV

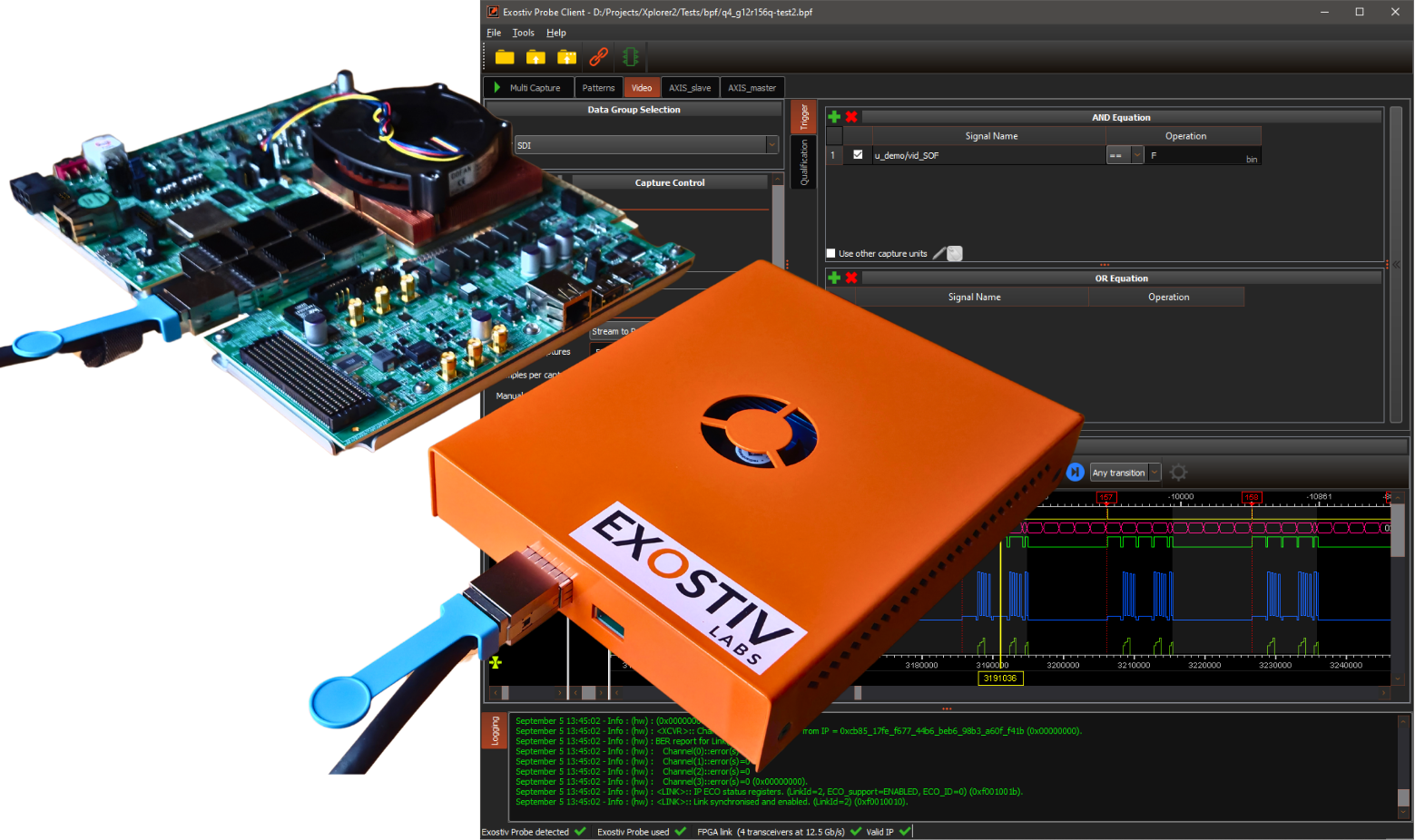

Massive FPGA Capture.

Monitor FPGA internal signals.

Visualize design operating at speed.

Benefits:

- Lower total engineering costs

- Allows at speed analysis of complex FPGA design placed in real environment

- Overcomes incomplete or flawed simulation-only approaches

- Adapts to any prototyping board

- Huge cost savings: no FPGA bugs in production

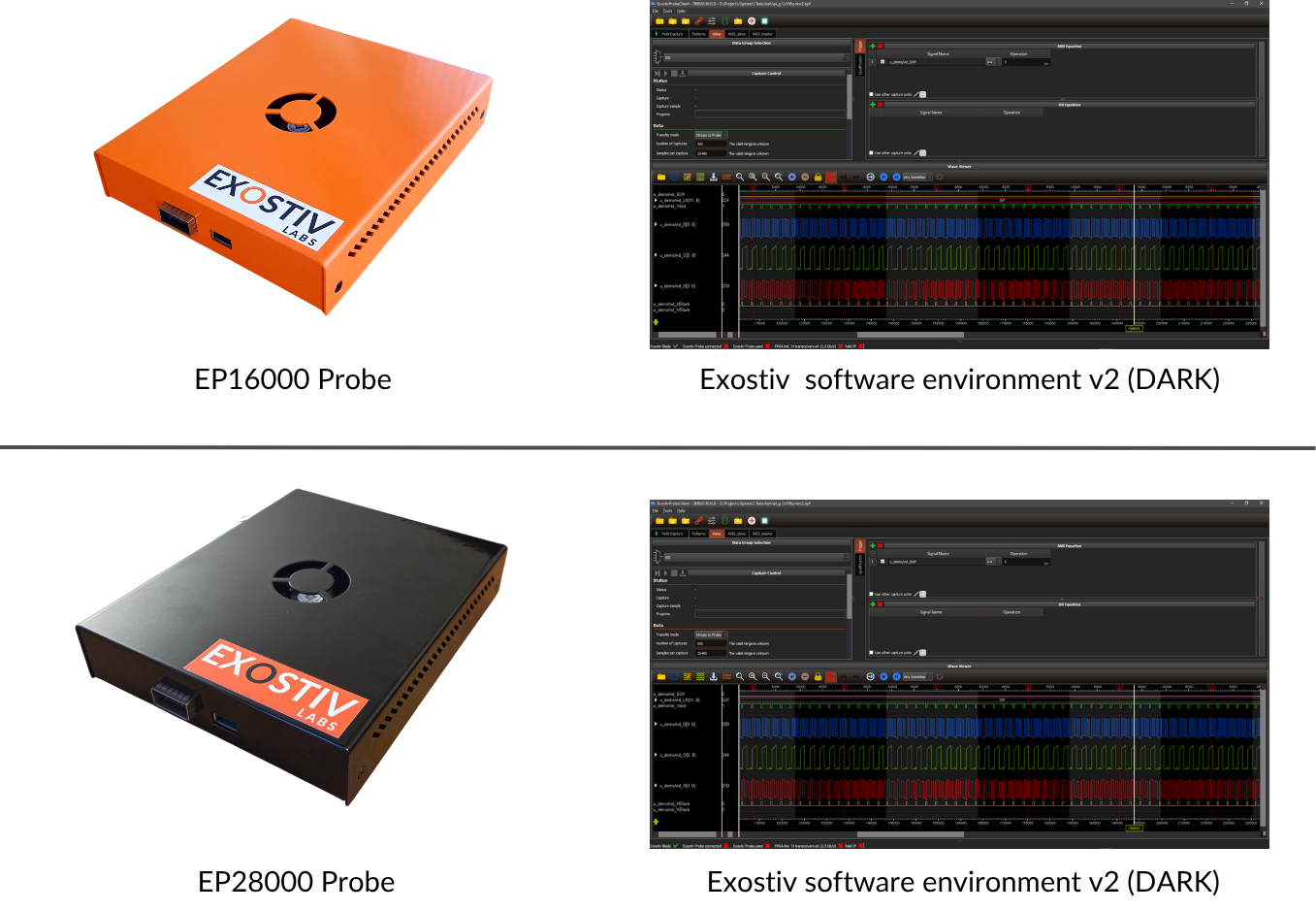

Exostiv Probes

Probe | EP28000 | |

Front panel connectors | QSFP28, Samtec ARF-6 | QSFP28, Samtec ARF-6 |

Number of transceivers | 4 | 4 |

Max. data rate per transceiver | 16.25 Gbps | 28.125 |

Total available bandwidth | 65 Gbps | 112.5 Gbps |

Capture memory | 8 GB | 8 GB |

Software environment | Environment v2 (DARK) – Exostiv Core Inserter – Exostiv Probe Client – Myriad, Ocean, Fusion | Environment v2 (DARK) – Exostiv Core Inserter – Exostiv Probe Client – Myriad, Ocean, Fusion |

Availability | Full production | Q2 2026 |

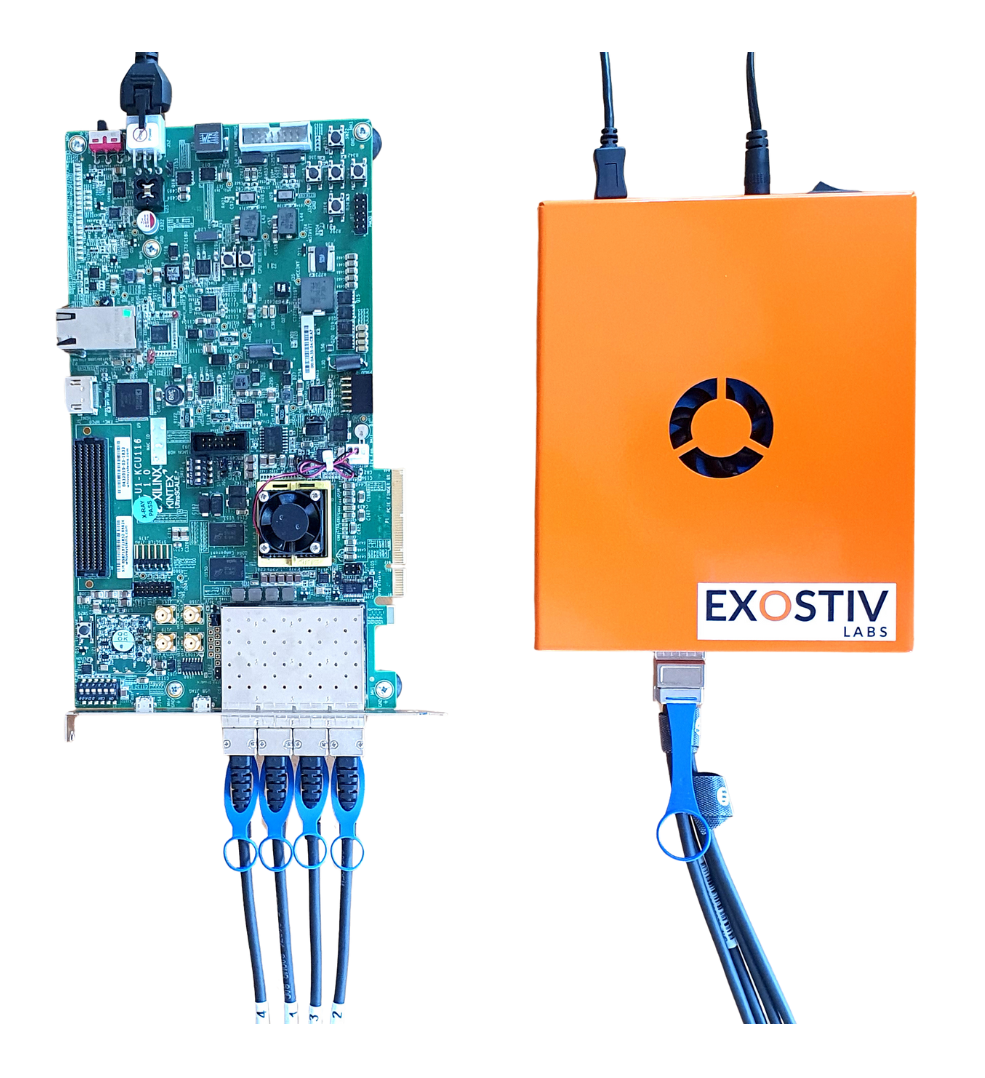

Connectivity

Download connecting guide (PDF).

Exostiv Probe EP16000 connects to FPGA chips transceivers, supporting up to 4 transceivers at 16.25 Gbps each (up to 65 Gbps per connector). EP28000 uses up to 4 transceivers at 28.125 Gbps each (up to 112.5 Gbps per connector).

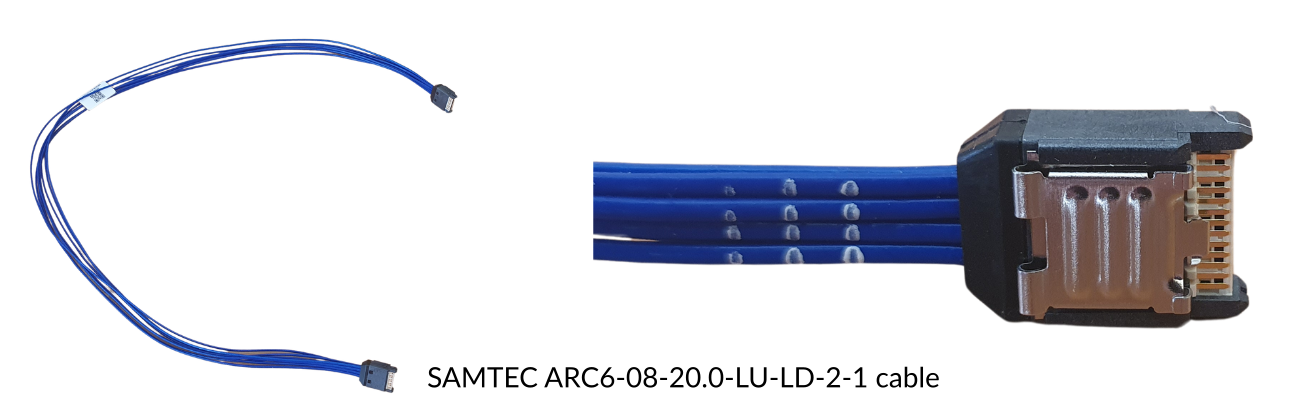

Exostiv Probe front panel provides 2 type connector types:

– QSFP28, compatible connectivity such as QSFP+, SFP28 or SFP+ with adapters are supported.

– SAMTEC ARF-6. This solution offers a small footprint connectivity solution for boards where space is limited. Cable reference part number: ARC6-08-xx.x-LU-LD-2-1.

Exostiv IPs overview

Exostiv offers a range of IP types tailored to accommodate diverse capture scenarios.

Exostiv Standard IP offers unparalleled flexibility, heightened interactivity in capture scenarios, and the fastest sampling speed, reaching up to 800 MHz.

With Exostiv Extended Width IP*, users can achieve the widest reach of up to 65k nodes while minimizing the impact on FPGA resources. By integrating multiple instances of either Exostiv IP, users can expand their node coverage even further within a single or across multiple FPGAs. Each IP instance uses from 1 to 4 FPGA transceivers.

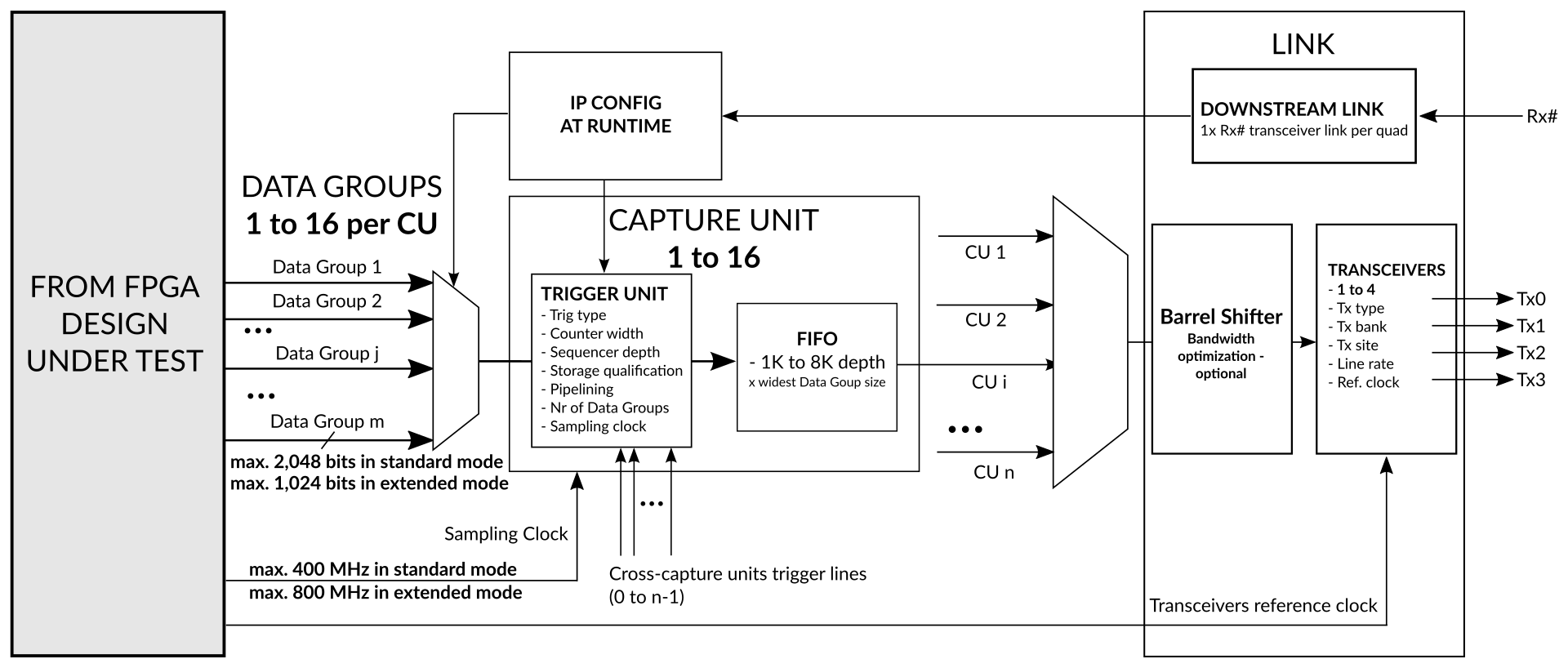

Standard IP

Main features include:

- Multiple capture unit with distinct sampling clock source

- Sampling up to 800 MHz

- Up to 16 x 2K bits simult. sampling per IP core instance

- Multiple data groups with dynamic selection at runtime

- Cross-clock domain triggering and data qualification

- Trigger positioning across the whole Exostiv Probe capture memory

- BRAM-based and Streaming (DDR based) modes of captures

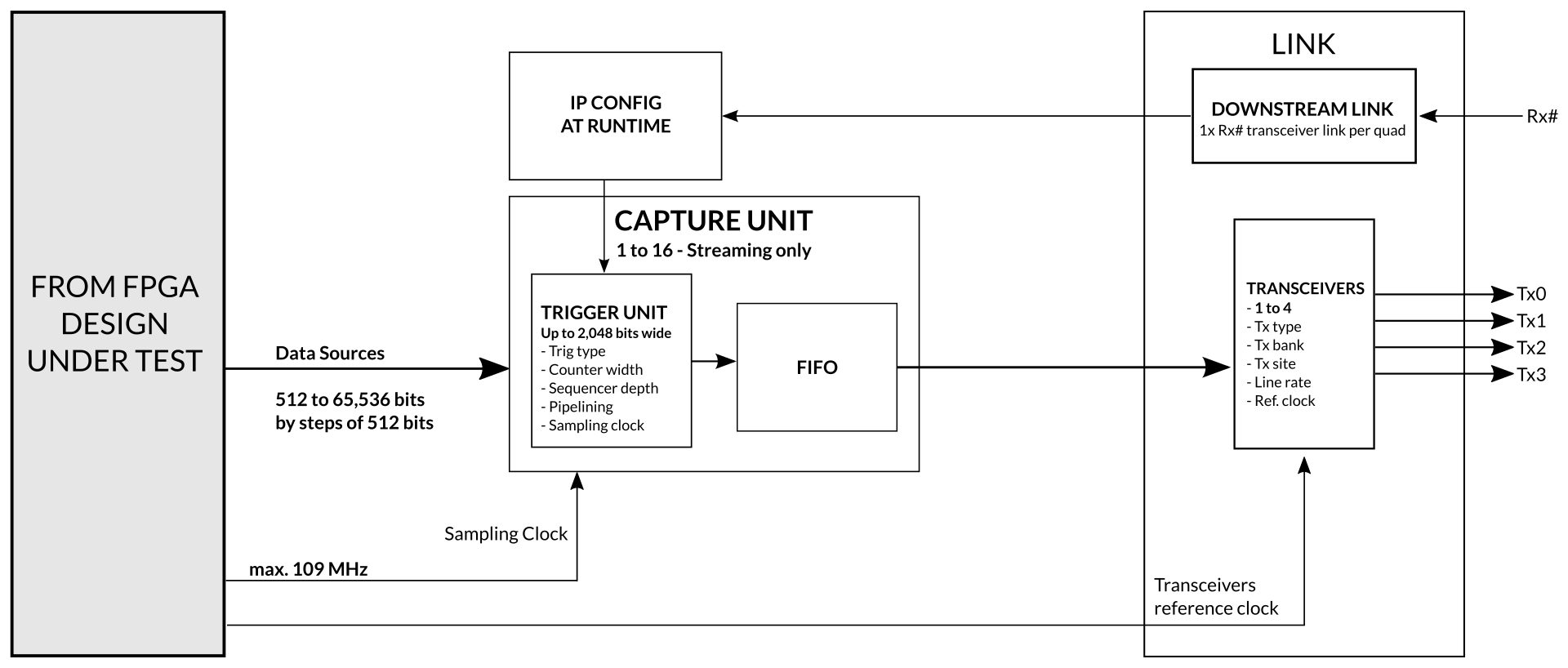

Extended width IP

Main features include:

- Multiple capture units with distinct sampling clock source

- Sampling up to 109 MHz

- Up to 65K bits simult. sampling per IP core instance

- Extremely small footprint.

- Triggering on up to 2,048 inputs

- Trigger positioning across the whole Exostiv Probe capture memory

- Streaming (DDR based) mode of capture

Exostiv IPs are configured, generated and inserted with the Exostiv Core Inserter software. Exostiv Core Inserter includes controls used to:

- Select the IP type.

- Define the location and settings of the FPGA transceivers used by the IP instance.

- Define the features and FPGA resources used by the IP.

- Set up the inputs ports of the IP instance and possibly select the observed nodes from the design under test.

- Generate and potentially insert the IP core into the target design.

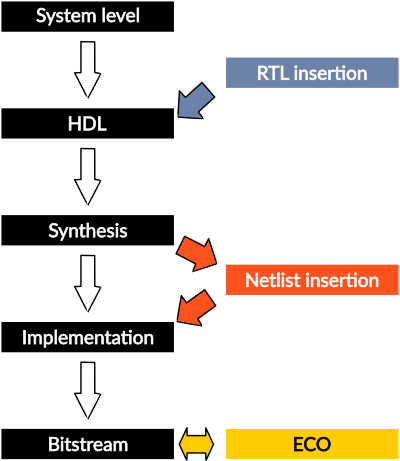

IP insertion flows

Exostiv core inserter enables IP generation, insertion and modification at 3 levels:

- RTL level: Exostiv IP instances are generated as a synthesized netlist with a VHDL or Verilog wrapper, design constraints and insertion template. The IP is inserted into the target design by the user like any other part of the design. Afterwards, the whole design has to be synthesized and implemented by the user. This mode of insertion provides full control to the user for insertion in the source code.

- Netlist level: (AMD FPGA only) Prior to proceeding with this type of insertion, the user has to load a post-synthesis design checkpoint in the FPGA vendor tool. Exostiv Core Inserter interacts with the vendor tool to select the sampling clock signals and the nodes to be observed with the Exostiv IP instance. Thereafter, Exostiv IP instances are synthesized and automatically inserted into the target design netlist. This is followed by automatic or manual implementation (P&R) and bitstream generation.

- ECO (Engineering Change Order – AMD FPGA only): This special level enables late modifications of the connections between a specific IP instance and the design under test. Prior to proceeding with it, the user has to load a post place and route DCP into the vendor tool. Exostiv core inserter interacts with the vendor tool to modify the existing connections with the FPGA under test. When the Exostiv IP resources need not to be modified, this mode provides the fastests turnaround time to observe new sets of FPGA nodes.

Exostiv – Technical specifications

Devices and Platforms

Supported FPGA devices* | AMD devices families: AMD Versal™ Adaptive SoCs, AMD UItrascale™+, AMD Ultrascale™, AMD Virtex™ 7, AMD Zynq™, AMD Kintex™ 7, AMD Artix™ 7 | |

Exostiv Probe connectivity | QSFP28, QSFP+, SFP28, SFP+, Samtech ARF-6 | Other connectors with adapter. |

PC connectivity | USB 2.0 and USB 3.0 | |

PC requirements | min. 8GB RAM available | |

OS Support | Windows, Linux | Win 64 versions 10 and 11. |

Features

Probe memory | 8 GB |

Connectivity | QSFP28, QSFP+ with standard cable SFP28, SFP+ with standard cable with splitter |

Number of transceivers | 1 to 4 |

Max. data rate per channel | 16.25 Gbps with EP16000 28.125 Gbps with EP28000 |

Max. sampling rate in FPGA | 800 MHz |

Max. nr of observable nodes | 32,768 with standard IP 65,536 with ext. width IP |

Max. nr of capture units / clock domains | 16 with standard IP 1 with ext. width IP |

Max. nr of FPGA nodes per capture unit | 2,048 with standard IP |

Min. FPGA memory per capture unit | 1 block RAM |

Data Groups multiplexing | Up to 16 groups per capture unit (standard IP) |

Triggering capabilities | Standard IP: Data qualification Concurrent triggering of 1 to 16 capture units.

Simple trigger capabilities – contact us for details. |

Capture modes | Stream to probe or burst to probe |

Synthesis / Implementation | Exostiv Core Inserter (Applies to AMD devices) Requires AMD Vivado™ 2019.2 to 2025.1 |

Insertion flow | (Applies to AMD devices) After synthesis (netlist level) Updates after P&R (ECO flow) |

Data visualization | With MYRIAD waveform viewer |

Data export | .vcd, .csv (text) and binary formats |