Search

In netlist insertion mode, how are nets preserved so they can be probed and not removed during logic optimization?

In ‘netlist insertion mode’, Exostiv Dashboard software uses Vivado to insert the configured Exostiv IP into the target design.

In this mode, the starting point is a generated netlist, whether Vivado synthesis or a 3rd party synthesizer is used.

The ability to preserve nets and net names depend on the synthesizer that was used to generate the netlist. Exostiv Dashboard does not have any influence on this.

Consequently, net (names) preservation really depend on the options chosen during synthesis.

Exostiv Dashboard software is able to detect the ‘mark_debug’ property provided by Vivado synthesis. This property allows marking the nets that you’d like to observe in the RTL code or in a constraints file. Doing so, the property *should* prevent Vivado from optimizing these nets and *should* force Vivado to keep the designated net name.

For more information on the mark_debug property: Xilinx UG936

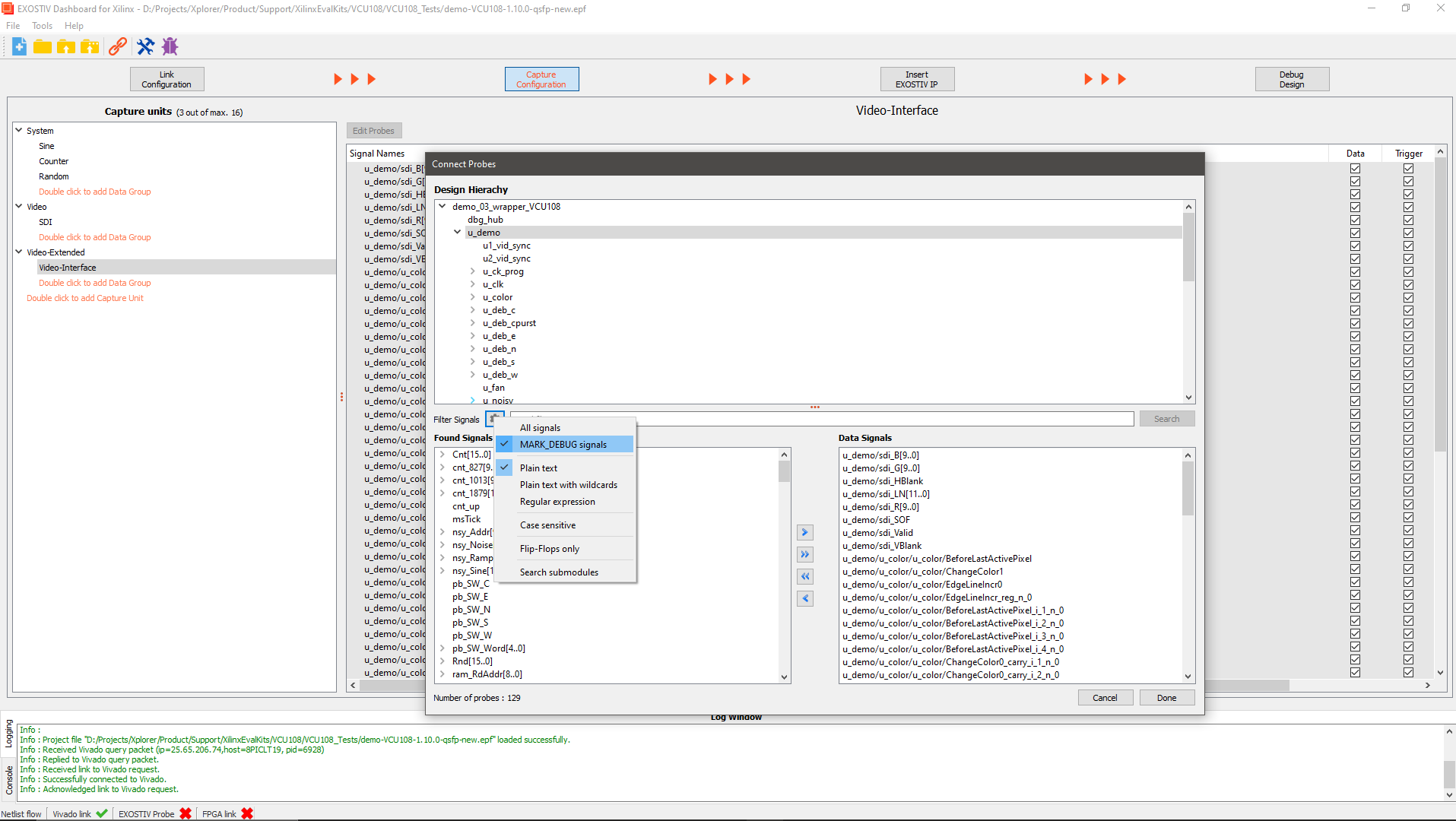

See screenshot below: the option to filter on the ‘mark_debug’ property is available from the ‘Edit Probes’ window of the Exostiv Dashboard core inserter in netlist insertion mode. To select a filter, click on the wheel next to the ‘filter signals’ box.