EXOSTIV lets you peer deeper into FPGA

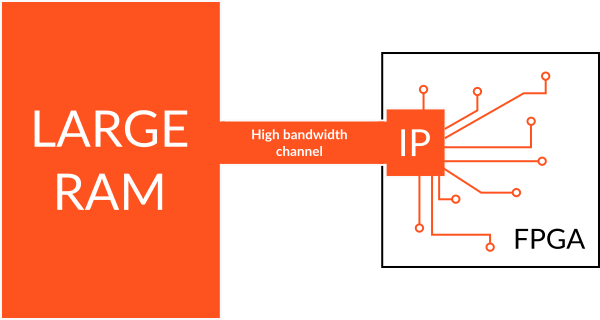

EXOSTIV‘s structure (see below) allows deeper data capture from inside FPGA: unlike JTAG instrumentation, EXOSTIV provides an external storage that extends beyond the memory available in the FPGA. Coupled with the usage of transceivers, it creates conditions in which data generated inside FPGA can reasonably be extracted on-the-fly – in bursts or continuously.

This structure brings significant advantages over the usual FPGA prototyping systems. Let’s review some of them.

1. Run prototype (and environment) at speed

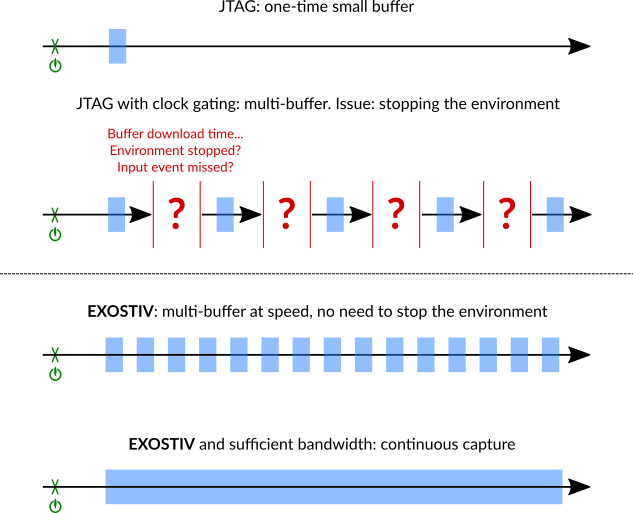

EXOSTIV’s competing tools usually leverage JTAG interfaces to access trace information stored into the FPGA. JTAG is available as a FPGA built-in resource and cheap to use from a board ‘real estate’ perspective, as a connector is readily available on the boards for other purposes. However, JTAG is (very) slow compared to the FPGA internal data production rate. Consequently, all the sampled trace must be stored somewhere in the system prior to reading it back – and no new data can be collected while the stored traces is retrieved.

With JTAG, the designer needs to accomodate for the small data quantity that can be squeezed in the leftover FPGA memory resources (no more than a few kilobytes). Some EDA vendors extend the reach on data of JTAG with clock gating control through JTAG. In this scenario, the system clocks are stopped each time an internal memory buffer is full to give the time to read them back.

Practically, FPGA execution pauses every 100 or 1000 cycles – so much for ‘real time execution’, as everything connected to the FPGAs must be stopped as well…

EXOSTIV inserts an IP into the design that makes use of the FPGA transceivers as a resource to stream data out of the chip as if it were a functional resource. In no case, the data flow in the FPGA is stopped. EXOSTIV requires that the average sampling bandwidth for traces does not exceed the bandwidth available at the transceivers level. Many strategies can be adopted to make the most of the available bandwidth – and mainly:

- Use capture units with various sizes: use a narrow capture unit to get a general view of key system signals of the FPGA, that can be captured continuously – and use wider capture units in bursts to look at specific details of the FPGA behaviour.

- Use data qualification, triggers and event counters to filter the sampled data down to the events that are really interesting for analysis. For instance, there is usually no interest in sampling a bus with no traffic.

Having more transceiver bandwidth is the way forward. Our current EXOSTIV product line provides up to 50 Gbps. Exostiv Labs currently works on new products that will provide much more bandwidth to extract traces from multiple FPGAs – more than 1,000 Gbps, with FPGA internal speeds up to 400 MHz (stay tuned for our future announcements). We target extreme visibility at speed of operation; this is why acting on the bandwidth is key to our product development strategy.

2. Explore the relationship between events separated over time.

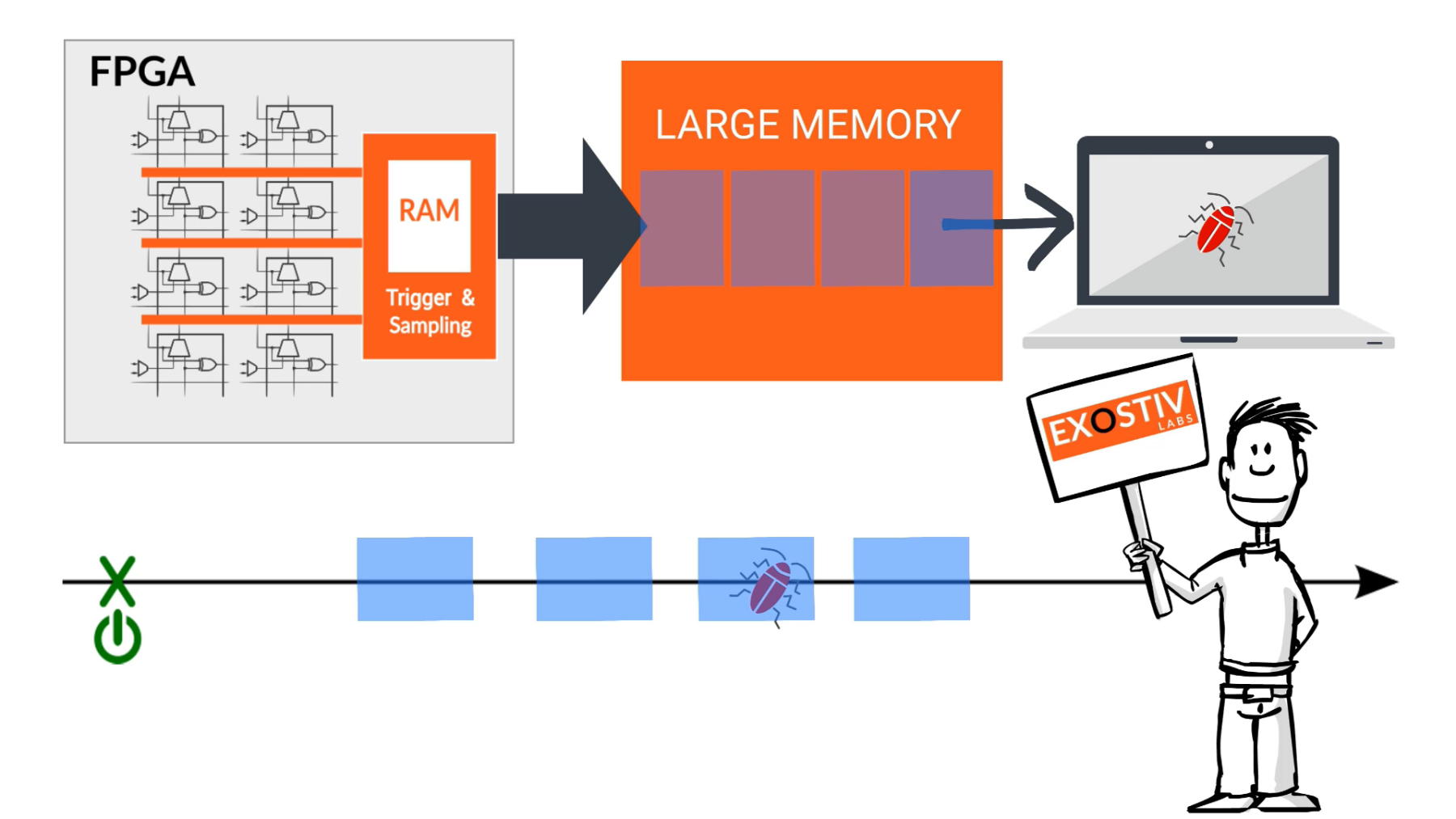

This case is illustrated by the picture below, taken from the video available above:

In this case, Exostiv is used to sample many of relatively small bursts over time. (For a demonstration of such a usage, please check this post and video, where we sampled the behaviour of an IP during more than one hour.).

With its large external memory (8 GB), EXOSTIV is able to run a capture that ends hours after it started. This can be especially useful for FPGA that manage large sequences of data over time, like crypto and security algorithms or video processing algorithms, where a bug can have effects a long time after. In such a case, being able to roll back extensively through the history of the FPGA behaviour is priceless.

3. Observe FPGA in realistic conditions during extended times

Beyond FPGA debugging, there can be a value to observe a prototype running during extended times. For systems-on-chip, for instance, it is sometimes difficult to properly size and organize the chip before some of the software is available and actually run on it. Simulation can help tremendously of course, but is inherently limited in time – and only as good as the modeled environment of the testbench. In addition, running system-on-chip software simulations is really time-consuming.

Which busses and resources will be under stress and which are sleepy; is there an interest to divide the system into subsystems, is it preferable to implement a DMA for some peripheral rather than letting the software move data? All this is more easily answered when there is a hardware available – the FPGA prototype – and some extended or statistical data of the system placed in a realistic environment. For this too, Exostiv Labs products are an invaluable resource that help collect large databases of such information in real time.

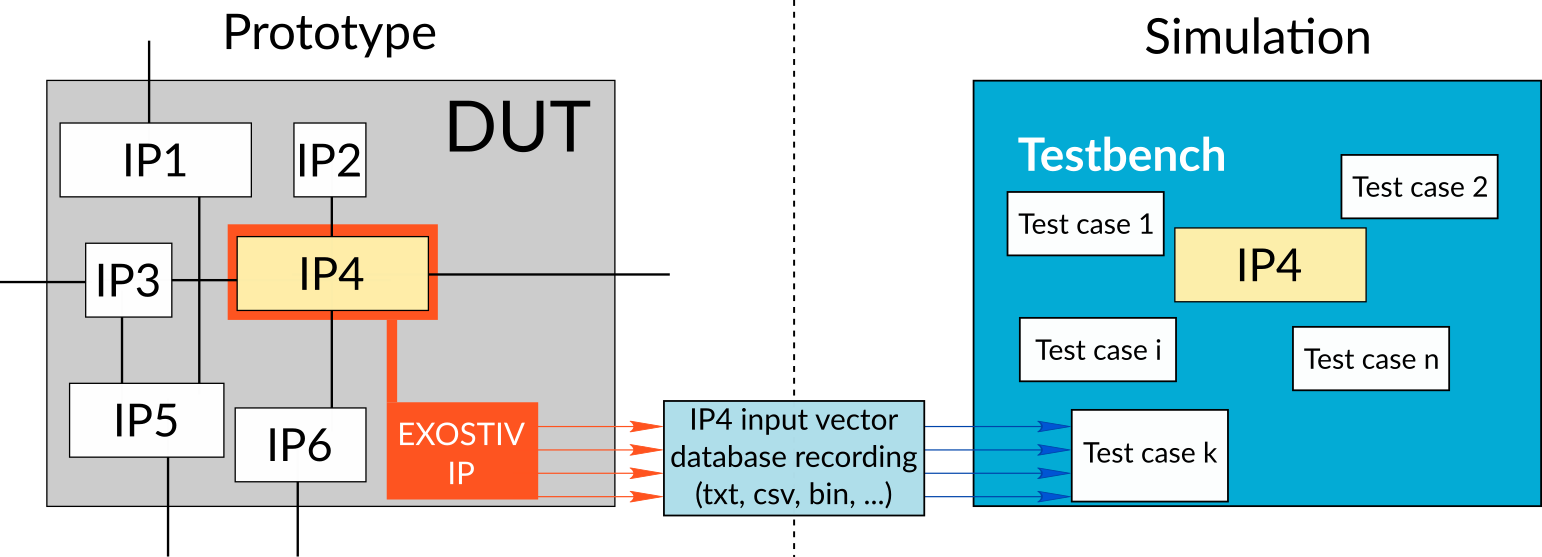

A similar usage consists in using Exostiv as a recorder of ‘input vectors’. In many instances, it is hard to build realistic models of the inputs that an IP will receive in reality. The chip environment often creates a complex combination of events that are rarely perfectly modeled in simulation. By placing a prototype in the future system environment and using EXOSTIV to record the inputs of a specific set of IPs, we can build realistic and extended databases of test vectors ready to be used in simulation. This is illustrated below and described more in details in this article.

Conclusion

Exostiv Labs solutions are built to provide very deep capture capability into the FPGA at speed of operation. Unlike competing solutions, our products let you see the internal behaviour of your FPGA or ASIC prototype during extended times without the constraint to modify or stop the target system environment. Exostiv Labs is committed to pursuing this target with its current and future solutions, providing more useful features and powerful hardware resources for FPGA product development and ASIC or SoC prototyping. Finally, with our board- and FPGA technology-agnostic solutions, you have the freedom to decide to make your board vs. buy it according to your requirements and budget.

As always, thank you for reading.

– Frederic.