Search

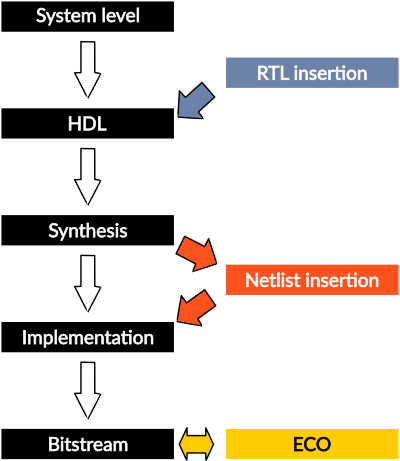

AMD Versal: insertion flows overview.

[one_half]

The contents of this article can also be found in the Exostiv Core Inserter user’s guide (PDF).

AMD Versal device support in Exostiv Labs products

For Exostiv Blade and EP16000 probe, AMD Versal devices are supported. From Exostiv Core Inserter version 2.1.0, Exostiv IP can be generated for Versal Gen 1 devices. Versal Gen 2 devices support are in the roadmap – please contact us for more details and availability.

As for other AMD devices, Exostiv Core Inserter allows Exostiv IP insertion into Versal devices at RTL and netlist levels, as well as a corrective ECO mode post place and route for further Exostiv IP connections modifications.

Versal flows, both in netlist mode and RTL mode, is slightly different from the corresponding flows for the other AMD devices families.

[/one_half]

[one_half_last]

[/one_half_last]

[divider]

Netlist flow for Versal devices

The Versal flow for the IP insertion in netlist mode differs from the other flow used for the other AMD/Xilinx FPGA families. Even if the Exostiv IP core is inserted and connected to the user’s design nets directly in the synthesized netlist, the transceiver bank used by the Exostiv IP must be inserted at RTL level in the user’s design.

The Exostiv IP generation and insertion is now performed in two steps.

- STEP 1: Generation of the Exostiv IP top level wrapper and the transceiver link.

- STEP 2: Generation and insertion of the Exostiv IP core.

This wrapper must be inserted in the user’s design at RTL level. HDL templates (‘.vo’ and ‘.vho’ files) are generated to help the user insert the IP top level wrapper in its code. When the wrapper is inserted in the user’s HDL, the generated TCL script to add generated files to the user’s design must be sourced from Vivado TCL console. A script is generated for project mode and for non-project mode Vivado usage.

Please select the script matching your case. This script generates a block design containing the transceiver link used by the Exostiv IP and adds all the required HDL files to the user’s design. At this point, the Exostiv IP top level contains two modules, the transceiver link and a dummy version of the IP core. This dummy core will be replaced by the real IP core during the netlist insertion step.

The synthesis can then be launched.

This step is performed after synthesis of the user’s design. After completing the core configuration and the selection of the nets to observe, the IP core is generated. It is then inserted in the user’s design netlist. Selected nets are automatically connected to the IP core. Implementation can then be launched.

[one_half]

Files generated by the Versal netlist flow:

File | Description / Usage |

Verilog files

| |

<instance_name>_core_dummy.v | Wrapper of the dummy IP core. |

<instance_name>_gt_wrapper.v | Wrapper for the transceiver link. |

<instance_name>_wrapper.v | Wrapper for the IP top level. |

<instance_name>_wrapper.vo | Template for top level insertion in user's design. |

VHDL files | |

<instance_name>_core_dummy.vhd | Wrapper for the dummy IP core. |

<instance_name>_gt_wrapper.vhd | Wrapper for the transceiver link. |

<instance_name>_wrapper.vhd | Wrapper for the IP top level. |

<instance_name>_wrapper.vho | Template for top level insertion in user's design. |

Constraint files | |

<instance_name>_wrapper_pinout.xdc | Constraint files defining the tarnsceiver pins mapping and reference clock. |

Scripts | |

Generate_gt_link_bd.tcl | Script generatingthe transceiver's block design. |

Non_project_mode_read_files.tcl | Script allowing adding all the generated files to the user design when non-project mode is used. |

Project_mode_add_files.tcl | Script allowing adding all the generated files to the user design when project mode is used. |

[/one_half]

[one_half_last]

Versal netlist flow, step by step:

Step nr | Tool | Step | Description |

1 | Core Inserter | Link configuration | Selects the target and setup transceiver. |

2 | Core Inserter | Exostiv IP Wrapper geenration | Generates RTL IP Wrapper for Versal devices |

3 | A code editor + Vivado | Insert the generated Exostiv IP Wrapper into the target design | To enable netlist insertion with versal device, the generated wrapper must be inserted into the target design and a script adds the required files to the Vivado project. |

4 | Vivado | Design synthesis | Synthesizes the target design with the generated wrapper. This wrapper instance allows the subsequent automatic insertion of the Exostiv IP. |

5 | Core Inserter | Capture configuration | Links Core Inserter to Vivado. Defines Exostiv IP resources, and input ports. Selects the nodes to be captured interactively from the loaded synthesized design. |

6 | Core Inserter | Insert Exostiv IP | Calls Vivado to synthesize the configured Exostiv IP. Inserts the synthesized IP into the synthesized target design. Optionally runs implementation (place& route, bitstream generation) |

7 | Vivado | (Optional): Instrumented design implementation and bitstream generation. | If not done at step 6, runs instrumented design implementation (place and route) and bitstream generation. |

[/one_half_last]

[divider]

RTL flow for Versal devices

The RTL flow is very similar to the first step of the netlist flow.

Instead of generating a dummy wrapper for the IP core, an EDIF netlist is generated. Using the generated templates, the user must insert the IP top level wrapper in its design at HDL level. In RTL mode, the nets to observe must be connected to the Exostiv IP wrapper. When the RTL insertion is done, the user must run the script corresponding to its Vivado use case (project mode or non-project mode) to generate the transceiver block design and add all generated files to its design. The RTL project is instrumented with the Exostiv IP core. Synthesis and implementation can be launched.

[one_half]

Files generated by the Versal RTL flow:

File | Description / Usage |

Verilog files | |

<instance_name>_gt_wrapper.v | Wrapper for the transceiver link. |

<instance_name>_wrapper.v | Wrapper for the IP top level. |

<instance_name>_wrapper.vo | Template for top level insertion in user's design. |

VHDL files | |

<instance_name>_gt_wrapper.vhd | Wrapper for the transceiver link. |

<instance_name>_wrapper.vhd | Wrapper for the IP top level. |

<instance_name>_wrapper.vho | Template for top level insertion in user's design. |

Netlist | |

<instance_name>_core_wrapper.edf | EDIF netlist of the Exostiv IP core. |

Constraint files | |

<instance_name>_wrapper_pinout.xdc | Constraint files defining the tarnsceiver pins mapping and reference clock. |

<instance_name>_core_wrapper.xdc | Timing constraints for the IP core netlist. This constraint must be scoped to the core wrapper module. |

Scripts | |

Generate_gt_link_bd.tcl | Script generatingthe transceiver's block design. |

Non_project_mode_read_files.tcl | Script allowing adding all the generated files to the user design when non-project mode is used. |

Project_mode_add_files.tcl | Script allowing adding all the generated files to the user design when project mode is used. |

[/one_half]

[one_half_last]

Versal RTL flow, step by step:

Step nr | Tool | Step | Description |

1 | Core Inserter | Link configuration | Selects the target and setup transceiver. |

2 | Core Inserter | Capture configuration | Defines Exostiv IP resources, and input ports. |

3 | Core Inserter | Generate Exostiv IP | Calls Vivado to generate the configured Exostiv IP. Saves synthesized IP, VHDL/Verilog module, constraints and scripts to an output directory. |

4 | A code editor | Design update | Target design update to instantiate the generated Exostiv IP. |

5 | Vivado | Call script generated with the code inserter. | Adds all the generated files to the user design in either project or non-project mode. |

6 | Vivado | Synthesis, implementation, bitstream generation. | Instrumented design generation. |

[/one_half_last]