Yes it does.

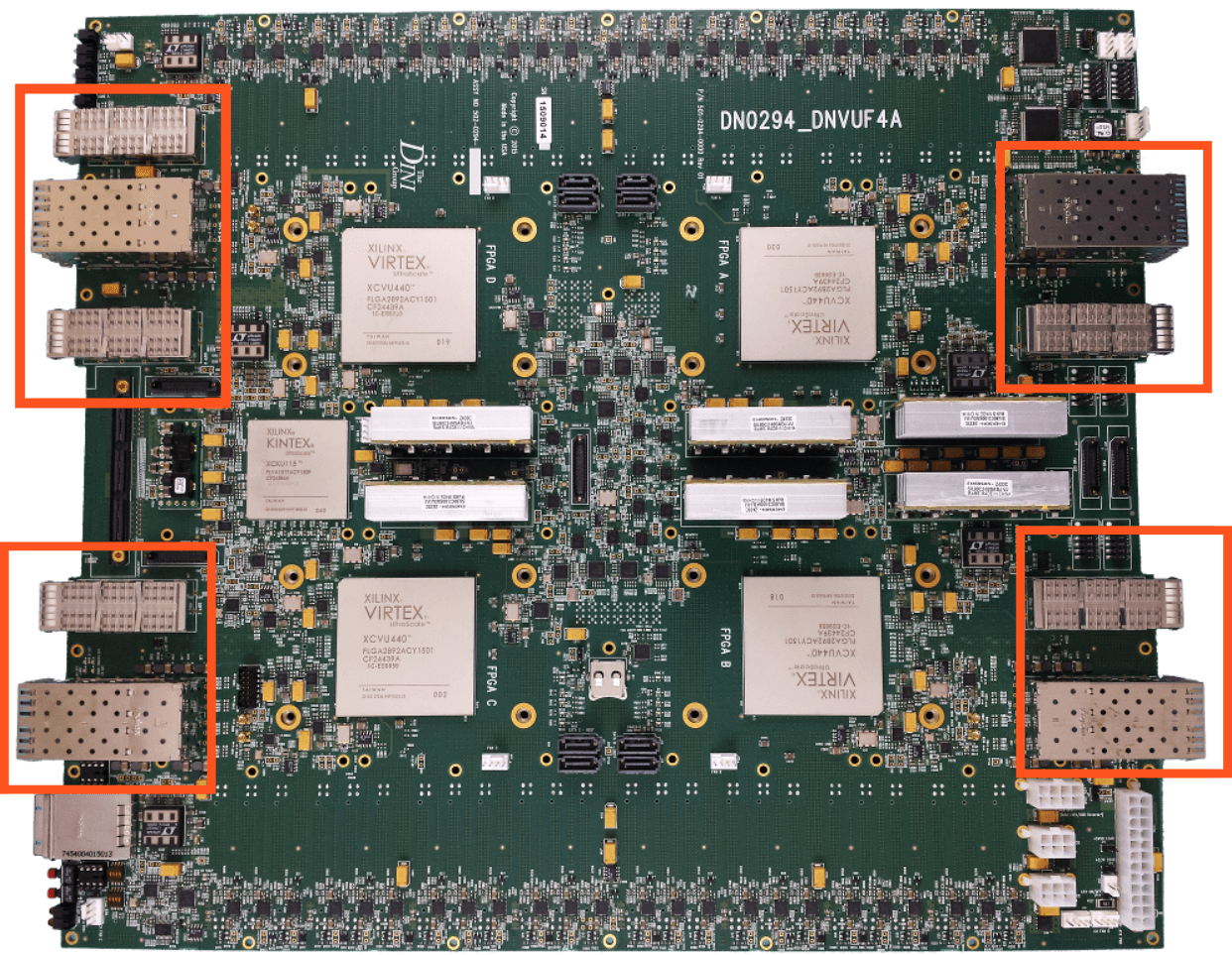

FPGA-based boards and systems are commonly used for prototyping ASICs and SoCs. They are usually composed of a series of boards with multiple FPGAs. An ASIC or a SoC can be prototyped by partitioning the design onto the FPGAs.

To use EXOSTIV with an ASIC / SoC prototyping system available from the market, the following aspects must be considered:

– How will EXOSTIV Probe be connected to the board?

– Which flow can be used to insert EXOSTIV IP in the prototyping system?

1) EXOSTIV connection to the board:

As explained here, EXOSTIV Probe provides multiple connection options with the target FPGA transceivers.

So the first step would be to check on which of the board’s high speed connectors a bank of transceivers is routed and available for access with EXOSTIV.

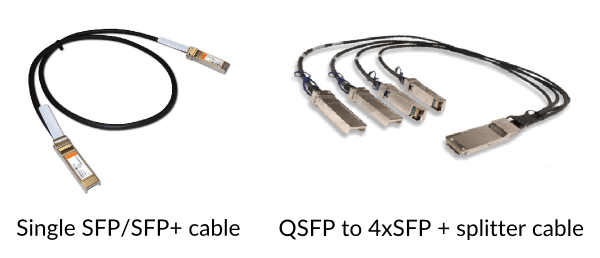

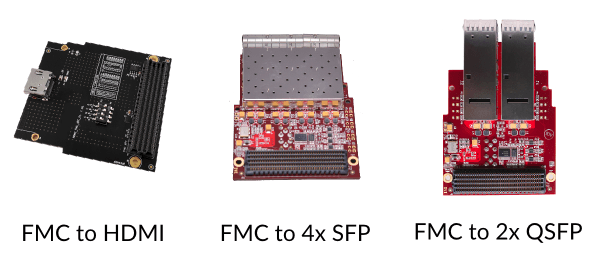

– If this connector is a standard FMC, SFP(+) or QSFP(+), then you’re all set: you’ll be able to connect EXOSTIV with SFP cables, QSFP to SFP cable with a splitter or with a FMC adapter.

– In addition, all ASIC prototyping system vendors provide adapters to add SFP/SFP+ or QSFP/QSFP+ (ans sometimes FMC) connectivity to their system. Such adapters are boards that are stacked onto the main board high speed connector and to provide high speed ports to the external world. EXOSTIV can simply connect to them. Please contact us or your board vendor if you are looking for a specific adapter.

Additional documentation: UG102 – EP Series Probes connecting guide (PDF)

– Each instance of EXOSTIV IP must be inserted in a single FPGA. All the IP resources, including the transceivers, must originate from a single FPGA.

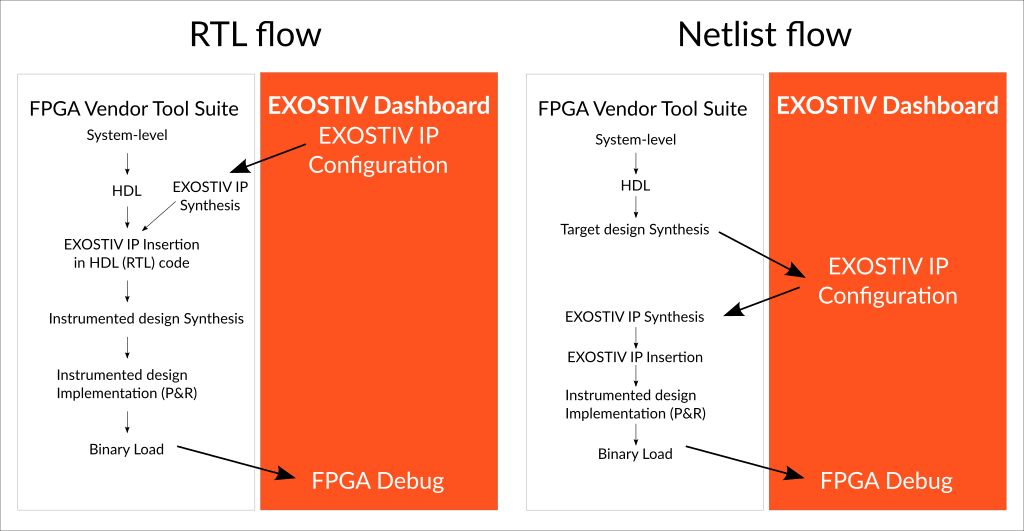

– When using the RTL flow:

- The generated EXOSTIV IP has to be inserted into the VHDL or Verilog code like any other functional IP – AND:

- Do NOT partition EXOSTIV IP onto multiple FPGA.

- You can insert EXOSTIV IP into a SINGLE FPGA netlist.

- Typically, you can partition your design onto multiple FPGA and synthesize each FPGA. After the synthesis of the FPGA you’d like to observe, you should interrupt the flow, load the synthesized design into Vivado and insert EXOSTIV IP into the loaded netlist. Then, you can finalize place and route and binary file generation.