Search

How much FPGA resources does Exostiv IP consume?

EXOSTIV IP is a highly configurable IP – here are the configuration options:

[one_half]

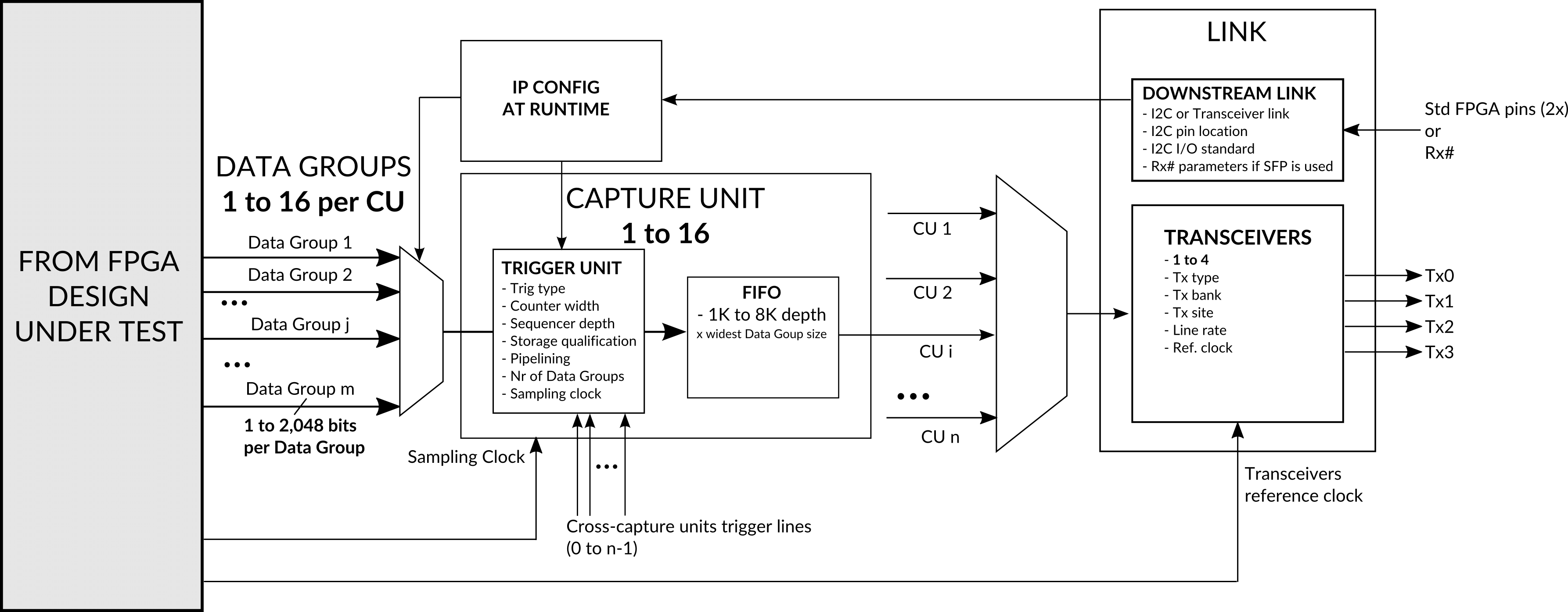

- 1 to 16 ‘capture units’;

- 1K to 8K sample of FIFO memory in *each* capture unit;

- 16 to 2,048 bits per sample for each data group;

- 1 to 16 multiplexed data groups in front of each capture counit;

- Optional features: complex triggering, data qualification, trigger counter, additional pipelining;

- Selectable sensitivity list for the trigger machine;

- 1 to 4 transceivers per IP;

[/one_half]

[one_half_last]

[/one_half_last]

Consequently, there is no single answer to this question.

[message]

In a first approach, we can say that Exostiv IP consumes about the same ***logic*** resources as Vivado ILA IP or Signal Tap IP for the same number of observed nodes.

Because of the structure of the whole Exostiv solution, the main gain over a traditional embedded logic analyzer solution that uses JTAG is in the memory resources.

Unlike JTAG Embedded logic analyzers, Exostiv does not keep the captured traces stored into the FPGA memory and hence, the size of the required memory does NOT grow with the size of the capture!.

[divider]

Xilinx FPGA: Click here to download some examples of IP complexities (PDF).

Intel FPGA: Click here to download some examples of IP complexities (PDF).

[/message]

! Please note ! Many strategies exist to make the most of the FPGA resources and yet reach unprecedented visibility. For additional examples and discuss the expected complexity of any Exostiv IP, please contact us, specifying the target device and the number of nodes that you’d like to observe.

[divider]

[message]

Further reading

Debugging FPGAs at full speed – An article about the strategies to use Exostiv to make the most of the resources available in the FPGA.

What are you ready to mobilize for FPGA debug? – An article about the tradeoffs of using FPGA resource to do a debug job.

Exostiv boosts RTL simulation. – An article about how properly combining Exostiv with simulation can boost your verification results!

[/message]