Search

Microchip FPGA: which files are produced in RTL flow and how do I use them?

Applies to IP generated with Exostiv Dashboard targeting Microchip devices.

Exostiv IP generated for Microchip FPGA has the following characteristics:

– the generation of the ‘logic’ part of the IP does not include the SERDES part of the IP;

– the SERDES part of the IP is generated as if the Exostiv IP was alone in using the chosen SERDES quad;

– along with the IP, Exostiv Dashboard provides a ‘standalone’ configuration block for the SERDES;

If the SERDES quad is used solely for the Exostiv IP, then the SERDES IP provided by Exostiv Dashboard can be used as is.

If the SERDES must be shared, inserting an generated Exostiv IP into an existing design can require from the user to:

– generate the SERDES IP separately so it can include the SERDES used for the Exostiv IP and SERDES used for another purpose in the design.

– adapt the FPGA configuration so it includes the settings for the SERDES used by the Exostiv IP.

It would be especially the case if a microcontroller is used for the configuration of the FPGA and/or there is an existing state machine block already included in the design to initialize other parts of it.

To ease the insertion process into the user’s design, Exostiv Dashboard provides an example design that the user can mimic to when proceeding with the Exostiv IP core insertion if this example design does not meet the SERDES configuration and characteristics of the target design.

[divider]

Which files are generated by Exostiv Dashboard for Microchip FPGAs?

Core files:

- <instance name>_wrapper.cxz : EXOSTIV IP synthesized netlist (without the SERDES).

- <instance name>_wrapper_pkg.vhd : VHDL package containing the EXOSTIV IP VHDL component declaration.

- <instance name>_wrapper.sdc : Timing constraints for EXOSTIV IP.

- <instance name>_wrapper_module.v : Verilog module for EXOSTIV IP netlist

- <instance name>_wrapper_import.tcl : Editable script used to import the EXOSTIV IP into the target project.

- SERDES.tcl : SERDES generation and configuration script.

- ‘./SERDES_CONFIG’ subdirectory : contains the configuration files for a SERDES module fully dedicated to be used with the generated Exostiv IP.

Example design files:

- <instance name>_exdes.sdc : Timing constraints for the EXOTIV IP, including the SERDES.

- <instance name>_exdes.vhd : Example design for Exostiv IP instantiation with SERDES and configuration modules.

- <instance name>_exdes_import.tcl : Import script to be used to generate the example design project in Libero.

[divider]

How to use the provided example design?

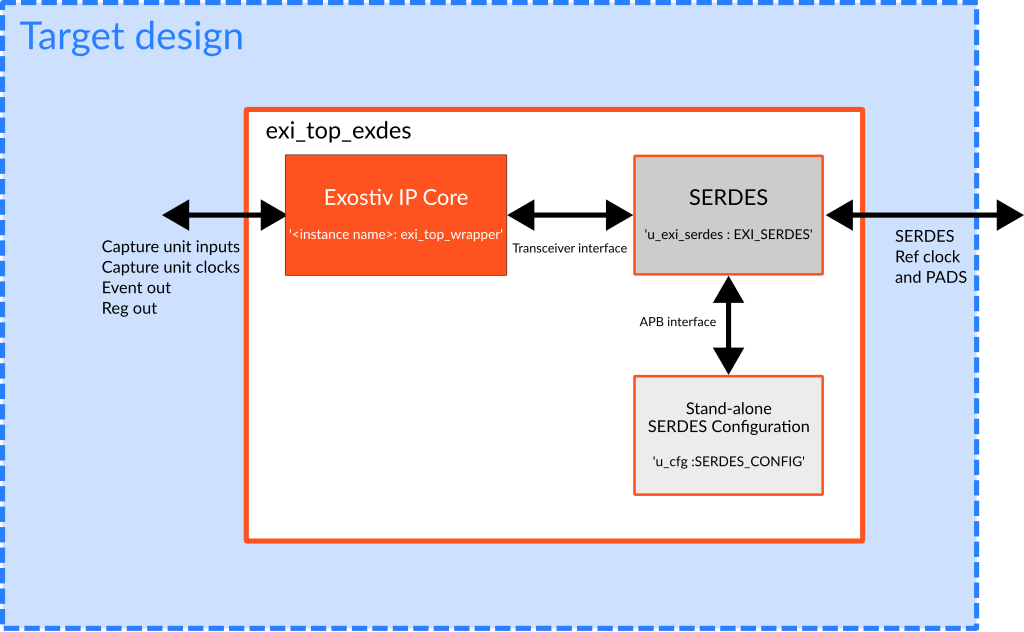

The provided example design shows how the generated Exostiv IP, the SERDES and the SERDES configuration module can be instantiated in a design. It supposes that the SERDES quad is fully used for the Exostiv IP and that the SERDES configuration module can be used with the target design.

To use the example design ‘as is’ in a target Libero project, please follow these steps:

- In the output directory where the Exostiv IP was generated, open and edit the file ‘<instance name>_exdes.sdc‘: replace the SERDES instance name field ‘<<<exdes_instance>>>‘ with the value ‘u_exi_serdes‘ – that is the instance name of the SERDES in the example design top ‘<instance name>_exdes.vhd‘;

- In the same file ‘<instance name>_exdes.sdc‘: replace the ‘<<<list_of_all_cu_clk>>>‘ field with the clock signals of the target design that will be used as sampling clocks for the respective capture units.

- Open the target Libero project where the Exostiv IP has to be inserted.

- From Libero, call script (File > Execute script) ‘<instance name>_exdes_import.tcl‘ to import file and build the Exostiv IP project hierarchy.

- At the desired level in the target project, add an instance of ‘exi_top_exdes’ and connect this module input ports to the design under test. Please refer to (reference) for a description of the Exostiv IP logic input ports.

[divider]

In this case, you must use Libero to generate the SERDES separately, that provides the connectivity and settings required for use with the generated Exostiv IP and the design functions that share the SERDES quad. When the SERDES module is generated, so is the configuration module and/or the microcontroller code for the SERDES configuration.

In order to be compatible with Exostiv IP, this SERDES module must be generated in EPCS mode and have 16-bit interfaces.

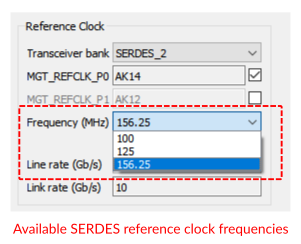

The SERDES reference clock should be supported by our IP (100 MHz, 125 MHz or 156.25 MHz – please submit a support ticket if you need another reference clock frequency for the SERDES). You can check the ‘Link Configuration’ tab in the Exostiv Dashboard software to check about the available SERDES reference clock values (see picture below).

[message]

Current valid SERDES configurations.

| SERDES mode | Ref Clock frequency | Interface | Data rate per lane | Remarks |

|---|---|---|---|---|

| EPCS | 100 MHz | 16 bits | 1.6 Gbps or 3.2 Gbps | 3.2 Gbps available on faster speed grade only. |

| EPCS | 125 MHz | 16 bits | 2 Gbps | |

| EPCS | 156.25 MHz | 16 bits | 2.5 Gbps |

[/message]

The following files only have to be imported into the target project:

- <instance name>_wrapper.cxz;

- <instance name>_wrapper_pkg.vhd;

- <instance name>_wrapper.sdc;

To do so, please use the following script: <instance name>_wrapper_import.tcl.

Modify the target design to connect the Exostiv IP to the design under test – see the file <instance name>_exdes.vhd for a code example.