Exostiv boosts RTL simulation It is essential to reduce the wasted machine cycles used for simulation workloads. Simulation dominates ASIC/SoC/FPGA verification process 'The 2020 Wilson Research Group ASIC and FPGA Functional Verification Study' reports that an ASIC, SoC or FPGA designer can spend up to 40% ofRead more →

Why we should scale FPGA tools - White Paper. In the 2020 edition of the Wilson Research Group Verification Survey [1], Siemens EDA, shows that a staggering 83% share of FPGA designs went to production with bugs in 2020. The results show that this share has remainedRead more →

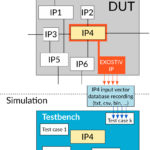

Record FPGA data during 1 hour - really. As ASIC, SoC and FPGA engineers, we are used to watching the operation of our designs based on single limited snapshots. RTL simulations, for instance, provide bit-level details during execution times that span over a few (milli)seconds at best.Read more →

Exostiv - Part 3 - Analyzer Demonstration This is the third and last part of a series of 3 posts that present our flagship product, Exostiv. This is the material that I use as an introduction to Exostiv; it is composed of 3 parts: - Part 1:Read more →

Choosing the ideal FPGA prototype for ASIC and SoC design - White Paper. In the 2020 edition of the Wilson Research Group Verification Survey, Mentor Graphics, a Siemens Business, shows that at least 30% of all respondents designing ASIC or SoC declare using FPGA prototyping, no matterRead more →