Delivering High Quality Semiconductor IP with confidence Because they are the essential building blocks of modern ASIC and SoC chips, semiconductor IPs are used in a wide variety of environments, in which they are in service during extended times. Verifying that they run flawlessly in all theseRead more →

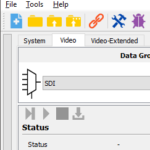

Exostiv - Part 3 - Analyzer Demonstration This is the third and last part of a series of 3 posts that present our flagship product, Exostiv. This is the material that I use as an introduction to Exostiv; it is composed of 3 parts: - Part 1:Read more →

Massive Real-time FPGA Data Capture A game-changer to prevent bug escapes to production. Welcome to this recorded session - thank you for your interest. If you are using AMD Ultrascale™(+) devices then you will be fully aware of the complexity of the designs these FPGAs can holdRead more →

Deep Trace & Bandwidth Exostiv provides the following maximum capabilities for capturing data from inside FPGA running at speed: Capabilities. 50 Gigabit per second bandwidth for collecting FPGA traces. 8 Gigabyte of memory for trace storage. 32,768 nodes probing simultaneously. 524,288 nodes reach. Actually, we have builtRead more →

Debugging FPGAs at full speed In my previous post, I explained why increasing the available 'window of visibility' is a gigantic advantage when tracking system-level issues on modern complex FPGAs. EXOSTIV's structure does not require the FPGA internal memory to grow with the depth of the capture.Read more →