Record FPGA data during 1 hour - really. As ASIC, SoC and FPGA engineers, we are used to watching the operation of our designs based on single limited snapshots. RTL simulations, for instance, provide bit-level details during execution times that span over a few (milli)seconds at best.Read more →

Exostiv - Part 2 - Core Inserter Demonstration This is the second part of a series of 3 posts that present our flagship product, Exostiv. This is the material that I use as an introduction to Exostiv; it is composed of 3 parts: - Part 1: Presentation,Read more →

Record 8GB from a running FPGA - really. In this blog post, I demonstrate 2 different - and extreme? - capture scenarios made possible with EXOSTIV. In the 2 cases, I have used a VCU108 Virtex Ultrascale development kit from Xilinx. (see Xilinx'coverage of EXOSTIV in theRead more →

Pick a FPGA board, please. Things to check before you use Exostiv... 'Using Exostiv requires having a board to which the Exostiv probe can be connected.' Of course. If you are considering using Exostiv, that's great, but you first need to check if the right kind ofRead more →

Deep Trace & Bandwidth Exostiv provides the following maximum capabilities for capturing data from inside FPGA running at speed: Capabilities. 50 Gigabit per second bandwidth for collecting FPGA traces. 8 Gigabyte of memory for trace storage. 32,768 nodes probing simultaneously. 524,288 nodes reach. Actually, we have builtRead more →

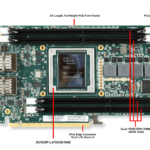

Announcing… EXOSTIV for Intel FPGA Using Intel FPGA? We have exciting news for you: EXOSTIV will soon support Intel FPGA! Please check the pictures above and below – this is EXOSTIV working with the ‘Attila’ dev kit of our partner, Reflex-CES, equipped with one Arria 10 GX

Read more →

Debug with reduced footprint Footprint, 'real estate', resources, ... No matter the design complexity, allocating resources to debugging is something you'll worry about. If you are reading these lines, it is likely that you have some interest in running some of your system debugging from a realRead more →