Search

I need a very specific trigger condition. What can I do?

EXOSTIV IP trigger resources allow defining conditions on signals and busses and combine them as AND and OR equations. The trigger condition can be configured at run time with the EXOSTIV Dashboard. This is done with the capture units’ trigger logic. Please refer to the user’s manuals for more details about triggers.

It is possible that the capture unit’s trigger logic is unable to implement specific trigger conditions.

Being able to define very accurate triggering conditions can be necessary, useful or just the result of an old habit. Please read the following considerations:

1) Please question your need to define a very complex triggering condition. In many cases, the need to define a very accurate condition results from a very ‘narrow’ observation window: as engineers we have been trained to think about what ‘exactly’ we wanted to capture because we could not afford to capture much… Think again: with the wide observation window provided by EXOSTIV, would it be possible to somewhat ‘relax’ the definition of the trigger and use a less accurate triggering condition? If it is possible to capture more data, isn’t it a good approach to be less accurate with the trigger and post-process data?

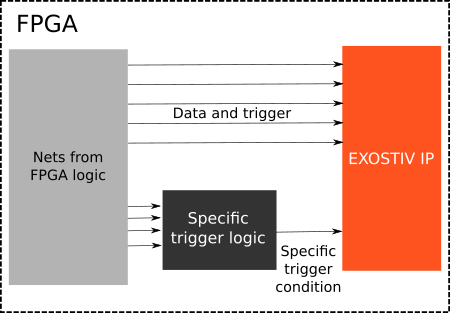

2) Can you insert the logic for detecting this specific condition and hook it up to one of EXOSTIV IP’s trigger lines (see picture below)? This approach provides full control over the trigger complexity that you want and that you can afford in terms of FPGA resources. All you have to do is design the specific trigger logic and state machine and use its results as a simple trigger line used from the EXOSTIV Analyzer.

3) If you have a suggestion, you can contact us.

We are always happy to receive your suggestions so EXOSTIV IP can evolve with your needs. However, covering more potential trigger cases is always a trade-off between the trigger flexibility and the complexity of it (= the FPGA resources usage).