What are the key features of ideal ASIC prototypes?

It seems that there has never been a better time to prototype IP, ASIC or SoC with FPGAs. With 35 to 40 billions transistors, the largest FPGA devices on the market can certainly hold quite some share of complex ASICs. Only at the start of 2021, the 3 major EDA companies have refreshed their offering for FPGA prototyping (see announcements from Synopsys, Siemens EDA and Cadence)

Prototyping ASIC or SoC primarily requires gates. If these gates can be enclosed in a minimum number of FPGAs, it is even better, as it reduces the need to partition the ASIC logic onto multiple FPGAs. Having coherent & complex sets of functionalities together limits the headaches related to having chip-to-chip interfaces to implement some of the internal logic of the ASIC. In addition, a smaller number of chips means higher running frequency, which we’ll evoke later.

Even though the FPGA technology is evolving towards more complexity per chip, choosing the right FPGA platform to prototype ASIC is challenging. Many aspects enter into consideration for this choice:

- Total number of gates;

- FPGA technology and size;

- Is the system modular and is modularity required?

- Will the system be used for one project only or multiple projects?

- Is there a software environment with tools to help with partitioning and/or debugging and verification?

- In which environment will the prototype have to operate?

- Will a purchased system be maintained and how to update its technology?

The question is: ‘What are the KEY features of ideal prototypes’?

We have isolated 2 among them:

The first key feature is called ‘Similarity to target’: an ideal prototype should run at operating speed, should provide the target device functionalities, and should run in the target environment.

The second key feature would be ‘Visibility’, that is, the ability to ‘look into the prototype in operation’. A totally opaque prototype is of no use: prototypes are used for debug, verification or even software development reasons. During these processes, being able to see how the prototype behaves – a bit like a simulation – is essential.

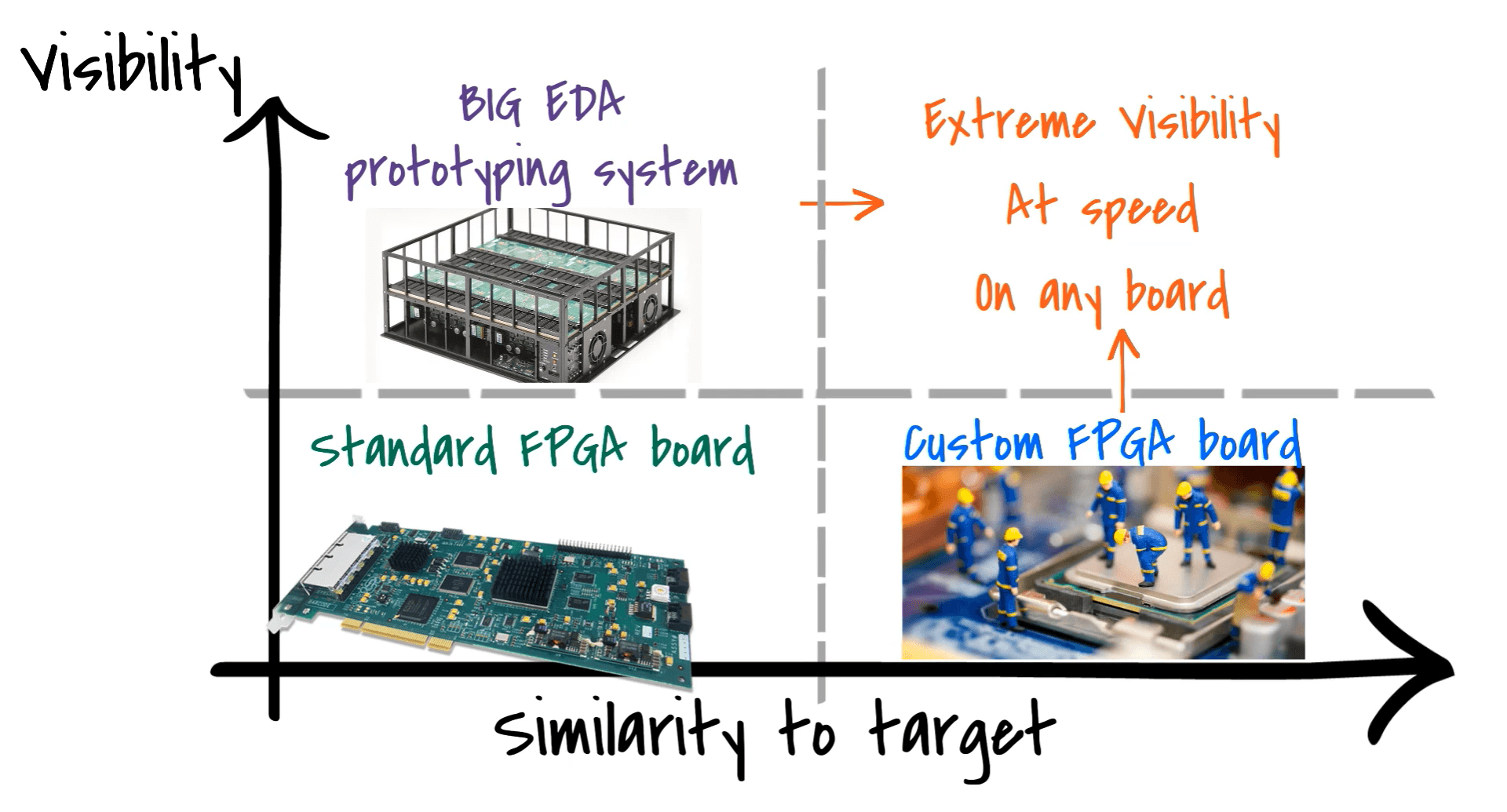

Let’s classify the various types of ASIC prototyping platforms according to these 2 criteria: similarity to target and visibility (see the chart below).

– Standard FPGA boards might not have the right set of components and peripherals to accurately behave like the target device. Especially when no more than 2 FPGAs are used to map the target ASIC, they could run close to the target speed. In addition, they come with no – or very limited visibility tools, often just traditional instrumentation or the JTAG-based embedded logic analyzer provided by the FPGA vendor. These tools prove to be very limited as for capturing the inner workings of the chips. For these reasons, such boards score low both on similarity and visibility.

– (Big) EDA companies provide sets of modular boards that can be assembled to to reach the desired number of gates and add peripherals in the shape of plug-in boards. These systems target ASIC prototyping and often come with additional tools to provide a much better visibility into the prototype.

However, such system could be bulky to use in some operating environments (like a car) and operate way below the target speed of operation, compromising operation in the target environments that cannot be slowed down. For instance if you need to check the compatibility of an interface IP with a series of existing devices, the IP prototyped on FPGA must run at speed!

– Building your own custom FPGA board provides full flexibility in terms of complexity, peripherals, features and often speed. As the board is specifically design for a specific ASIC target, the latest FPGA technology can be used (while your re-used prototyping system can have aged a little…). It might not be re-usable for another project, like a modular prototyping system, but that would be the price of a good score on ‘similarity’, both in terms of features, ability to run in the target environment and speed!

Unfortunately, like their standard equivalent, custom FPGA boards are not provided with the set of tools ready to be used to gain visibility. Designing custom tools is usually not reasonable nor very realistic (budget, engineering time, maintenance, …) for a team already busy with a full ASIC or SoC design.

What would be the ideal prototype?

Ideally, we should occupy the remaining quadrant of the above chart: this is a solution that scores high both for the similarity to the target (and we have found that this means: similarity in features AND speed) and for the visibility.

What we need is:

- Total freedom of choice for the board(s): an ability to chose the target FPGA technology to make the most of the latest and greatest FPGA chips, having just the right set of features, peripheral and ability to integrate the board into the target environment;

- At speed operation, as this is one of the keys to be able to test the prototype against a realistic set of inputs, coming from an environment that does not need to be artificially slowed down because an imperfect prototype requires it!

- Extreme visibility into the prototype, to be able to look into and see the prototype operate with full details.

Reach maximal visibility on any type of ASIC prototype.

The Exostiv series and the Exostiv Blade series provide unprecedented visibility into any type of prototyping platform, no matter if you use standard boards, advanced prototyping systems or even custom boards. Our tools are constantly upgraded to support the latest technologies from major FPGA vendors and connect to your prototype through standard interfaces and flows. Bottom line: you are not locked anymore into using an outdated FPGA technology, a specific FPGA vendor or a previously purchased but unfit prototyping system.

Have total freedom of choice for your prototype: you can even use the same visibility tools with a succession of prototyping platforms along your validation journey. Choosing or designing your own FPGA prototyping platform does not mean ‘poor visibility’ anymore!

As always, thank you for reading.

– Frederic.

(Originally published in 2021)