Record FPGA data during 1 hour - really. As ASIC, SoC and FPGA engineers, we are used to watching the operation of our designs based on single limited snapshots. RTL simulations, for instance, provide bit-level details during execution times that span over a few (milli)seconds at best.Read more →

You can capture tons of data. Now what? Offering huge new capabilities is not always seen positively. Sometimes, engineers come to us and ask: 'Now that I am able to collect Gigabytes of trace data from FPGA running at speed... how do I analyze that much data?'.Read more →

Did you know that Exostiv can send triggers across clock domains? 'Visibility into the FPGA' is a multi-dimensional notion. Obviously, it means 'being able to watch' the inner workings of the chip - and hence, acquire the broadest (over)view on the FPGA. Today, we'll cover another aspectRead more →

Exostiv provides Gigabytes of visibility into the FPGA running at speed of operation from virtually any board. In this webinar, we'll introduce and demonstrate Exostiv and show how it can boost productivity when designing, debugging and verifying FPGA - and this, whether you use FPGA for ASICRead more →

On-Demand Webinar: 'How to capture Gigabytes of traces from FPGA. At speed.' In this post, you have the opportunity to catch up with our Webinar that ran live earlier this year. In this -now 'on-demand'- webinar we introduce and demonstrate EXOSTIV and show how it can boostRead more →

Exostiv provides Gigabytes of visibility into the FPGA running at speed of operation from virtually any board. In this webinar, we'll introduce and demonstrate Exostiv and show how it can boost productivity when designing, debugging and verifying FPGA - and this, whether you use FPGA for ASICRead more →

Exostiv provides Gigabytes of visibility into the FPGA running at speed of operation from virtually any board. In this webinar, we'll introduce and demonstrate Exostiv and show how it can boost productivity when designing, debugging and verifying FPGA - and this, whether you use FPGA for ASICRead more →

Exostiv provides Gigabytes of visibility into the FPGA running at speed of operation from virtually any board. In this webinar, we'll introduce and demonstrate Exostiv and show how it can boost productivity when designing, debugging and verifying FPGA - and this, whether you use FPGA for ASICRead more →

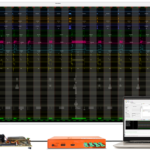

Deep Trace & Bandwidth Exostiv provides the following maximum capabilities for capturing data from inside FPGA running at speed: Capabilities. 50 Gigabit per second bandwidth for collecting FPGA traces. 8 Gigabyte of memory for trace storage. 32,768 nodes probing simultaneously. 524,288 nodes reach. Actually, we have builtRead more →

EXOSTIV is there – and it is not a monster As you might have noticed, EXOSTIV for Xilinx is now released. With the launch, I have been on the roads to demonstrate the product. The good thing about meeting FPGA engineers is the flurry of questions, ideas

Read more →