What are the key features of ideal ASIC prototypes? It seems that there has never been a better time to prototype IP, ASIC or SoC with FPGAs. With 35 to 40 billions transistors, the largest FPGA devices on the market can certainly hold quite some share ofRead more →

Exostiv Blade - Managing multiple sites, targets & users In this video, we demonstrate that Exostiv Blade lets you manage multiple sites, target boards and users to reach your FPGA debug, verification and test goals. In a previous demonstration, we already showed that Exostiv Blade core capabilitiesRead more →

Upgrading FPGA Prototyping for High RTL Debug Productivity The importance of FPGA prototyping Despite important advances in simulation-based validation and emulation, ASIC engineers worldwide keep on using FPGA prototyping systems. Earlier this year, we have seen the launch of a new generation of such systems from multipleRead more →

Exostiv Blade - Core capabilities demonstration Here is a follow up of what was announced in our introductory article about the main features of Exostiv Blade. Down below, you can find the recording of a demonstration of Exostiv Blade in which we have wanted to show 2Read more →

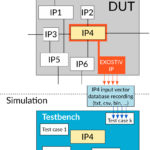

Exostiv boosts RTL simulation It is essential to reduce the wasted machine cycles used for simulation workloads. Simulation dominates ASIC/SoC/FPGA verification process 'The 2020 Wilson Research Group ASIC and FPGA Functional Verification Study' reports that an ASIC, SoC or FPGA designer can spend up to 40% ofRead more →

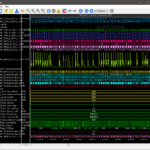

Our new waveform viewer is 10x faster! I am happy to announce that Exostiv Dashboard 1.10.0 has been released this week. In addition to the usual maintenance on supporting new devices, new versions of FPGA tools, and a discreet yet fresh icon set update, this is theRead more →

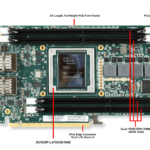

FPGA prototyping platform gets visibility with EXOSTIV This month, thanks to AVNET Israel, we received the ONIX platform for interoperability tests. The board that we received was the AVT-ONIX-VU440-1, equipped with 1 Xilinx Virtex Ultrascale XCVU440 device. The ONIX board system is designed by DgTronix in IsraelRead more →

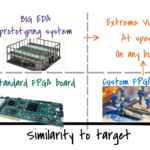

The FPGA Prototyping problem we are trying to solve 'A la Carte Menu' or 'Full Course Dinner'? Today, choosing a FPGA-based prototyping platform for ASIC or SoC design reduces to 2 choices: - Either you buy or build a FPGA board and choose EDA tools separately; or:Read more →

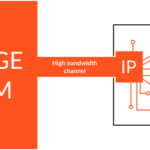

EXOSTIV lets you peer deeper into FPGA Watch now... EXOSTIV Introduction EXOSTIV's structure (see below) allows deeper data capture from inside FPGA: unlike JTAG instrumentation, EXOSTIV provides an external storage that extends beyond the memory available in the FPGA. Coupled with the usage of transceivers, it createsRead more →

Pick a FPGA board, please. Things to check before you use Exostiv... 'Using Exostiv requires having a board to which the Exostiv probe can be connected.' Of course. If you are considering using Exostiv, that's great, but you first need to check if the right kind ofRead more →